Imagens de suporte

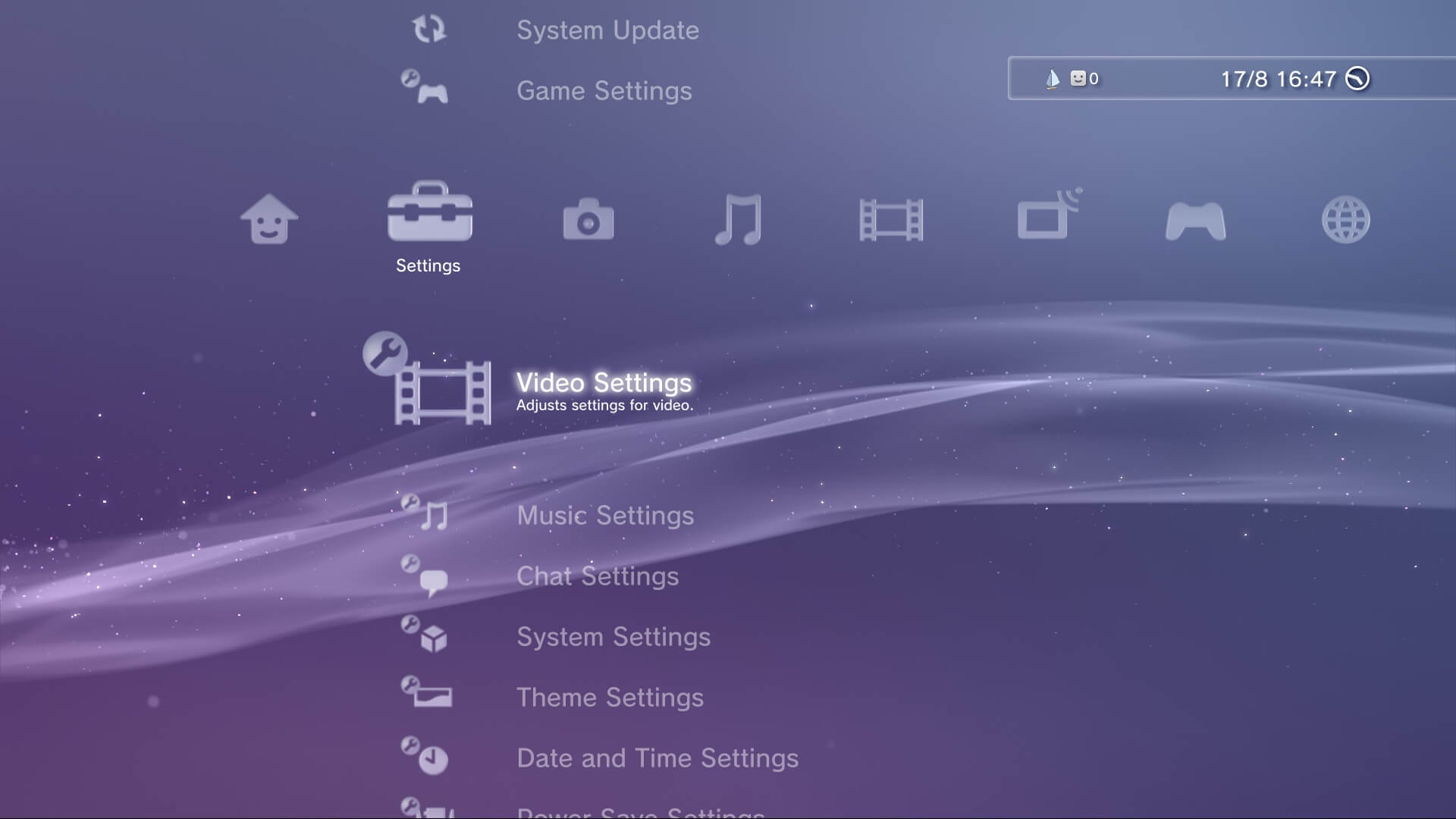

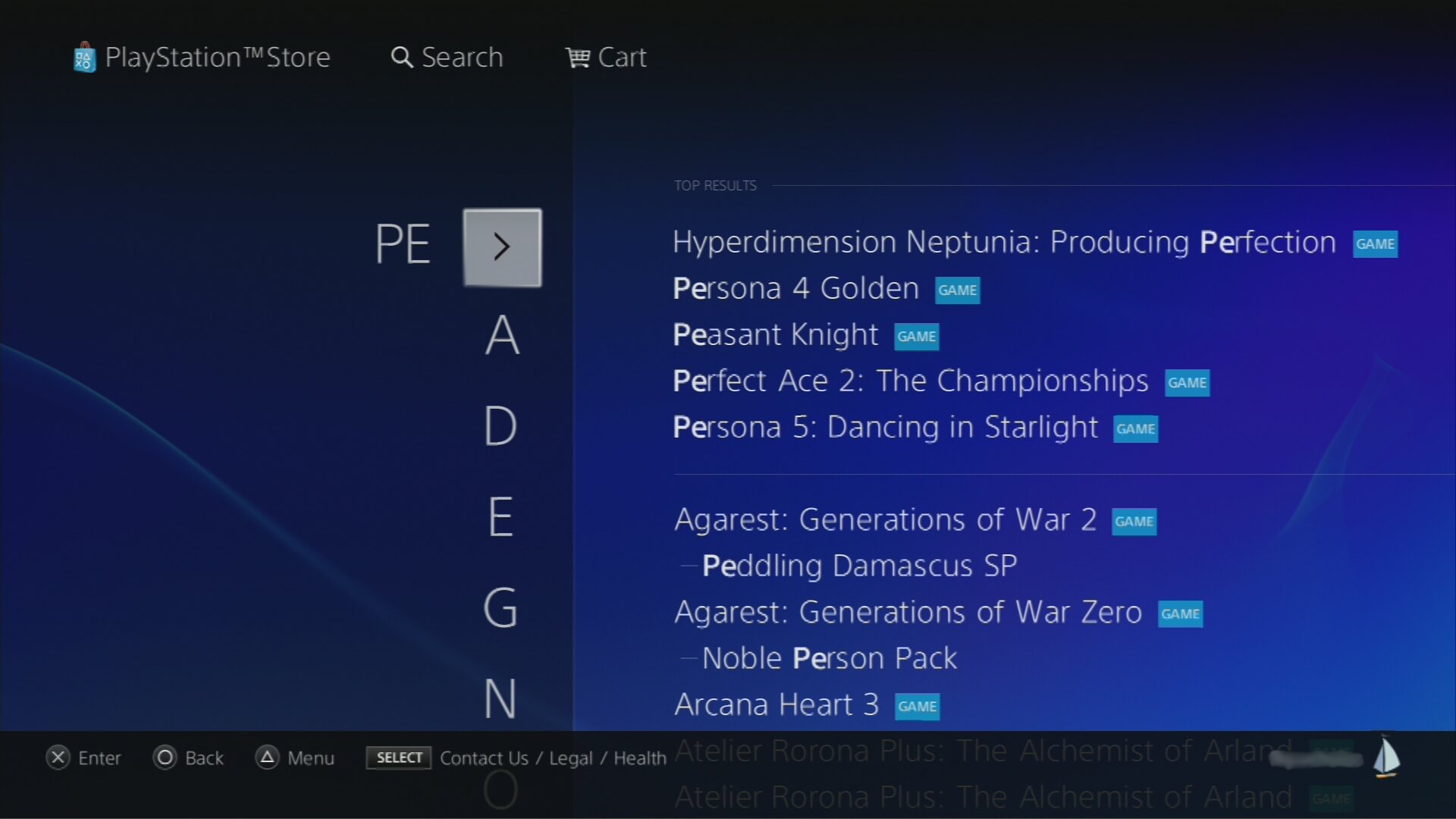

Modelo

Lançado em 11/11/2006 no Japão, 17/11/2006 na América e 23/03/2007 na Europa

Lançado em 01/09/2009 na Europa e América; e 03/09/2009 no Japão

Lançado em 09/2012 internacionalmente

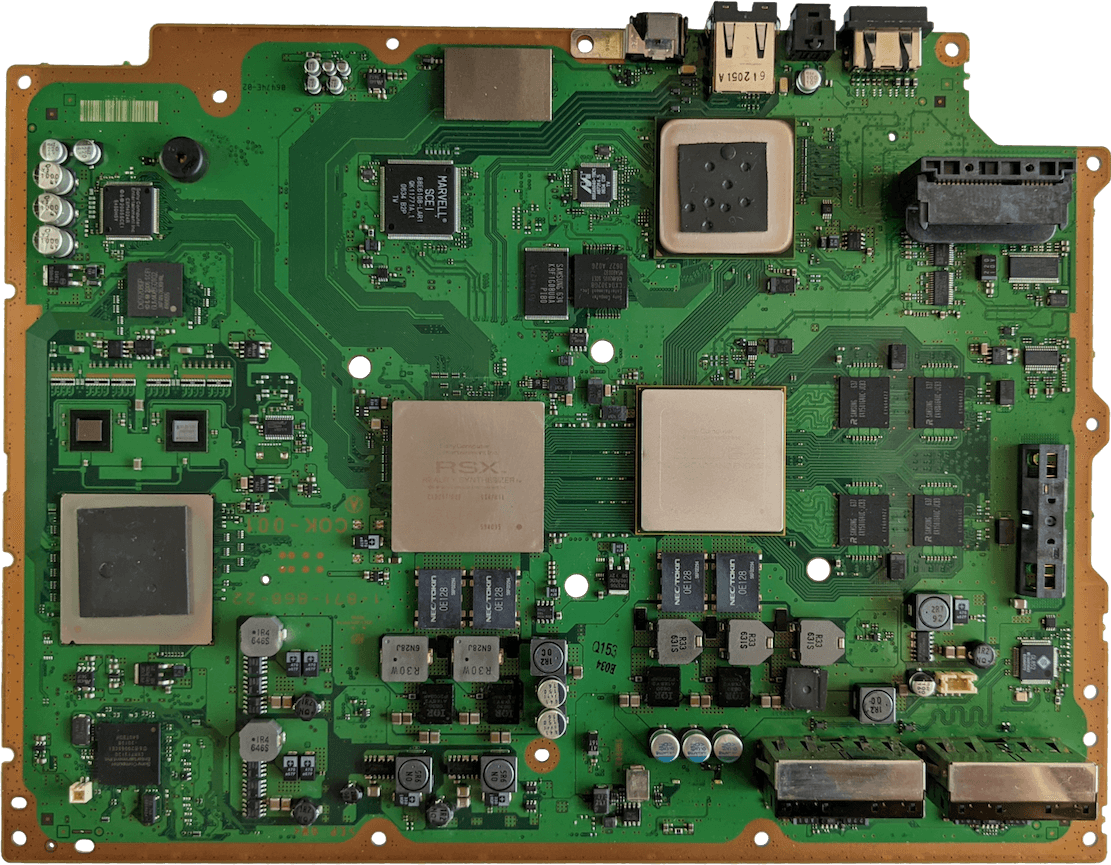

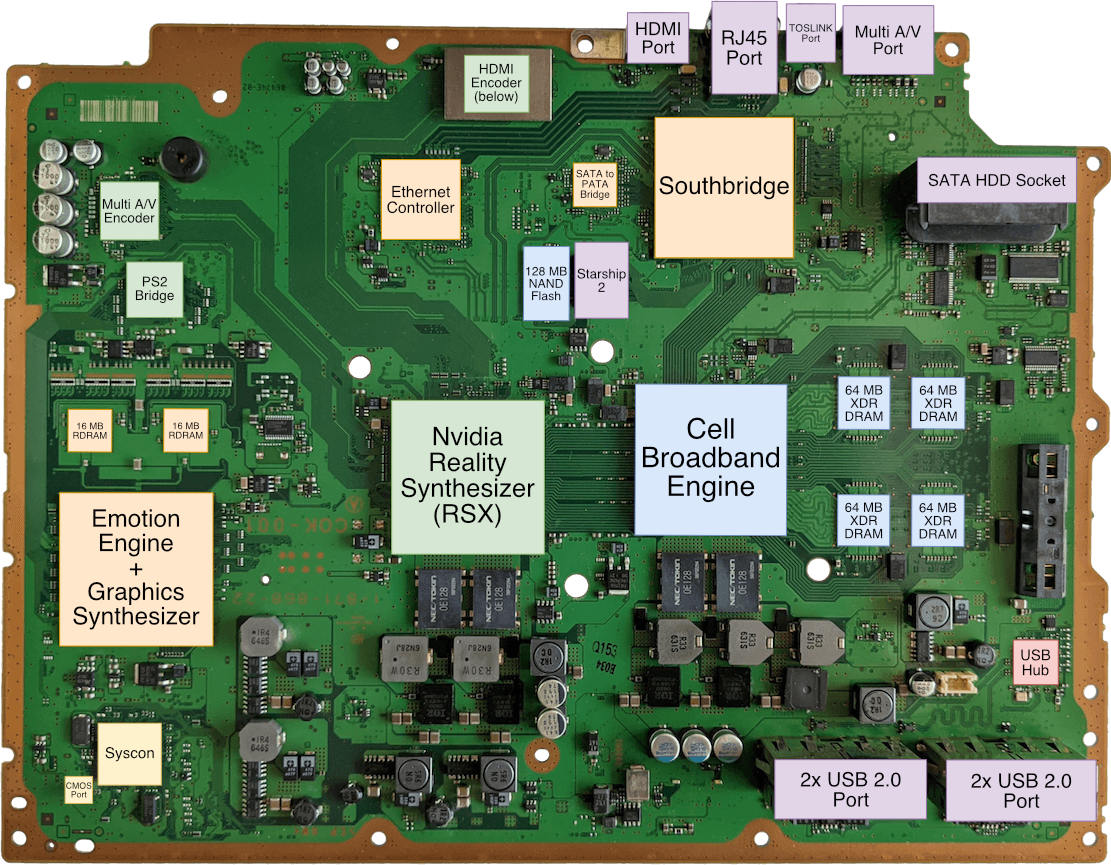

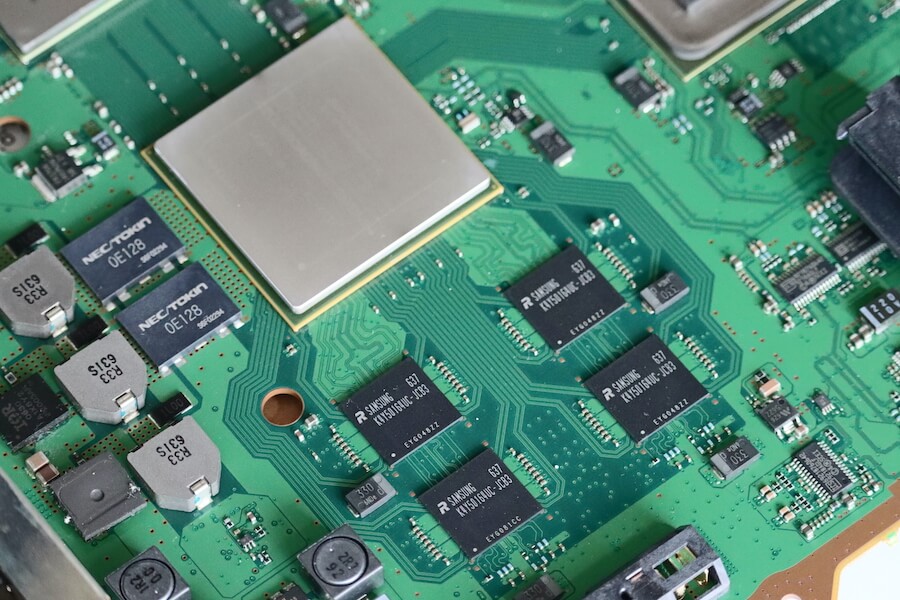

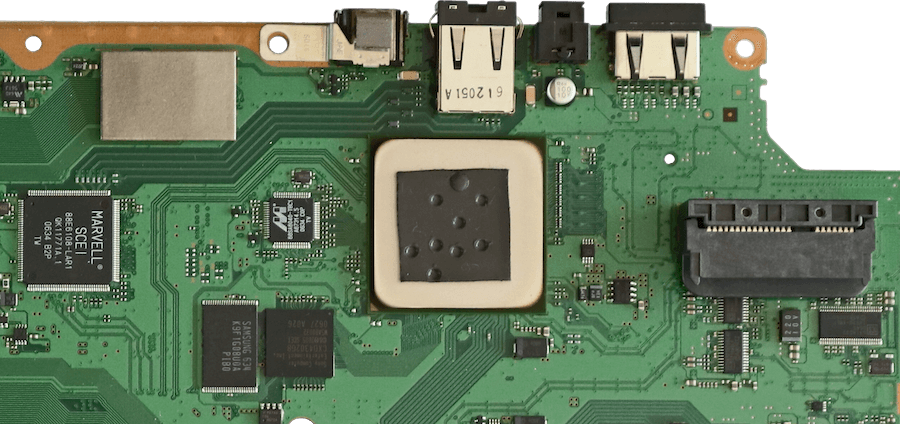

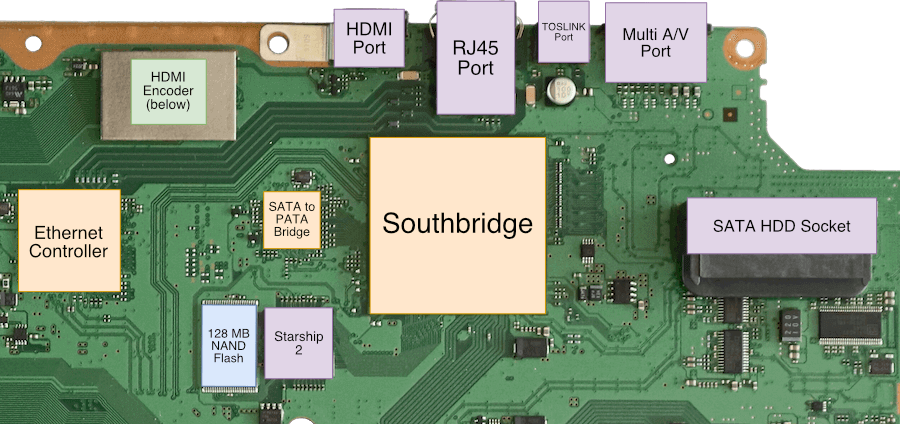

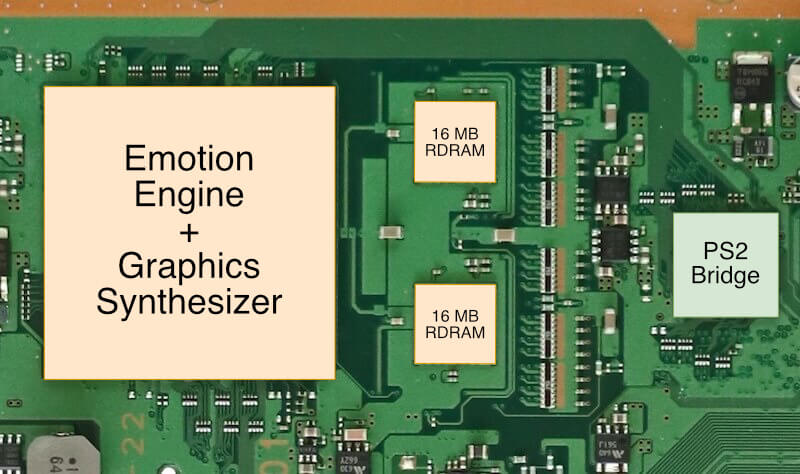

Placa-mãe

Exibindo a revisão COK-001 (a primeira), retirada do meu modelo CECHA12.

Os conectores para a unidade Blu-ray PATA, placa-filha Wifi/BT, painel frontal e leitor de MultiCard, e os 128 MB de memória Flash NAND, estão localizados na parte de trás

Diagrama

Uma breve introdução

Em 2006, a Sony revelou o tão esperado console de videogame de “próxima geração”, uma máquina brilhante (embora pesada) cuja a arquitetura base do hardware continua os ensinamentos do Emotion Engine, ou seja, foco no processamento de vetores para obter poder, mesmo com o custo da complexidade. Enquanto isso, o seu novo “super processador”, o Cell Broadband Engine, é concebido durante uma crise de inovação e terá que acompanhar as tendências dos serviços multimídias à medida que eles evoluem.

Este artigo examina em profundidade o projeto de parceria da Sony, IBM, Toshiba e Nvidia, junto a sua execução e o efeito na indústria.

Sobre o tamanho do artigo

Receio que este artigo não seja o típico “intervalo de almoço” que eu geralmente escrevo para os outros consoles desta série. Se você estiver interessado em todas as áreas do PlayStation 3, prepare-se para uma jornada completa! Dito isso, esta redação abrange cerca de 6 anos de pesquisa e desenvolvimento realizados por incontáveis engenheiros, então não espero que você digira tudo de uma vez. Por favor, leve o seu tempo (e faça pausas, se necessário) e se, no final ainda quiser mais, consulte a seção de “Fontes”!

CPU

Bem-vindo à parte mais conhecida e inovadora deste console.

Introdução

A CPU do PS3 é extremamente complexa, mas também é um trabalho de engenharia muito fascinante que cruza necessidades complexas e soluções incomuns, proeminentes em uma era de mudanças e experimentações. Então, antes de mergulharmos nos detalhes da CPU do PS3, escrevi os próximos parágrafos para trazer um contexto histórico. Dessa forma, conseguiremos decompor o chip de cima a baixo de uma maneira que não só permitirá que você entenda como este chip funciona, mas também compreenda a lógica por trás das principais decisões de projeto.

O estado do progresso

Quase dez anos após a introdução do PlayStation original com processador MIPS, no início dos anos 2000, as coisas não pareciam boas para a CGI/MIPS. A Nintendo tinha recentemente abandonado os processadores MIPS em favor de um núcleo PowerPC de baixo custo com a IBM como novo fornecedor, enquanto a Microsoft, a novata deste mercado, escolheu a Intel e seu império x86.

A Sony tinha um histórico de pegar projetos existentes de baixo custo (núcleos MIPS baratos) e moldá-los para alcançar um desempenho 3D aceitável com custo reduzido, um processo que envolveu outras empresas, como a LSI (para a CPU do PS1) e a Toshiba (para o Emotion Engine do PS2). Esse método continuou até 2004 com o lançamento do PlayStation Portable. Então, qual seria a nova combinação de MIPS que eles iriam construir para o PlayStation 3?

Bem, acontece que o desenvolvimento do PlayStation 3 precede o do PlayStation Portable [1]. Em 2000, meses após o lançamento do PS2, a Sony formou uma aliança com a IBM e a Toshiba chamada “STI” com o único objetivo de entregar o próximo chip que poderia alimentar a próxima geração de supercomputadores [2]. Se isso já não parecesse extravagante o suficiente, o próximo chip também seria usado no sucessor do PS2. No final, em 2004, a IBM apresentou o Cell Broadband Engine (também conhecido como “Cell BE” ou simplesmente “Cell”) [3].

Novas filosofias de projeto

Para entender a proposta radical, devemos primeiro considerar dos problemas que afetavam aquela época (final dos anos 90 e início dos anos 2000).

A cada ano, os consumidores pediam mais velocidade. Isso sempre foi assim. No entanto, a última abordagem utilizada para resolver isso (construir um pipeline no caminho de dados e aumentar a frequência do clock) estava falhando em escalar. O NetBurst da Intel não pôde evoluir mais e seu prometido sucessor não existia. Da mesma forma, o PowerPC 970/G5 da IBM não pôde cumprir sua promessa de “3 GHz” nem de sua CPU ser de baixo consumo de energia (daí a Apple não conseguir lançar nenhum laptop com sua CPU da última geração) [4]. Resumindo, parecia que os engenheiros tinham uma nova crise de escalabilidade em mãos.

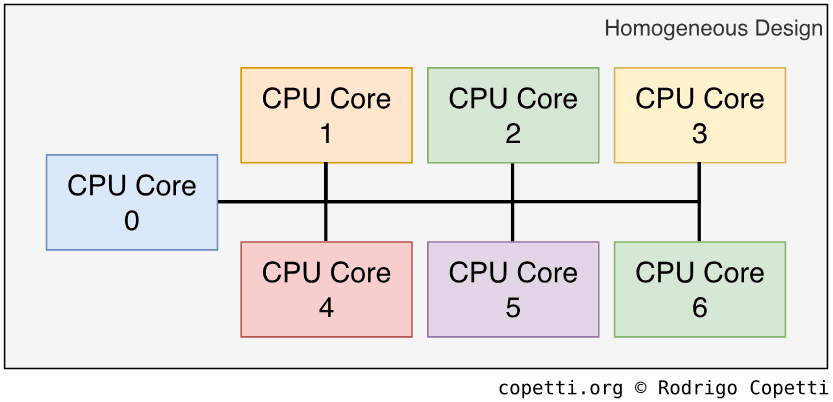

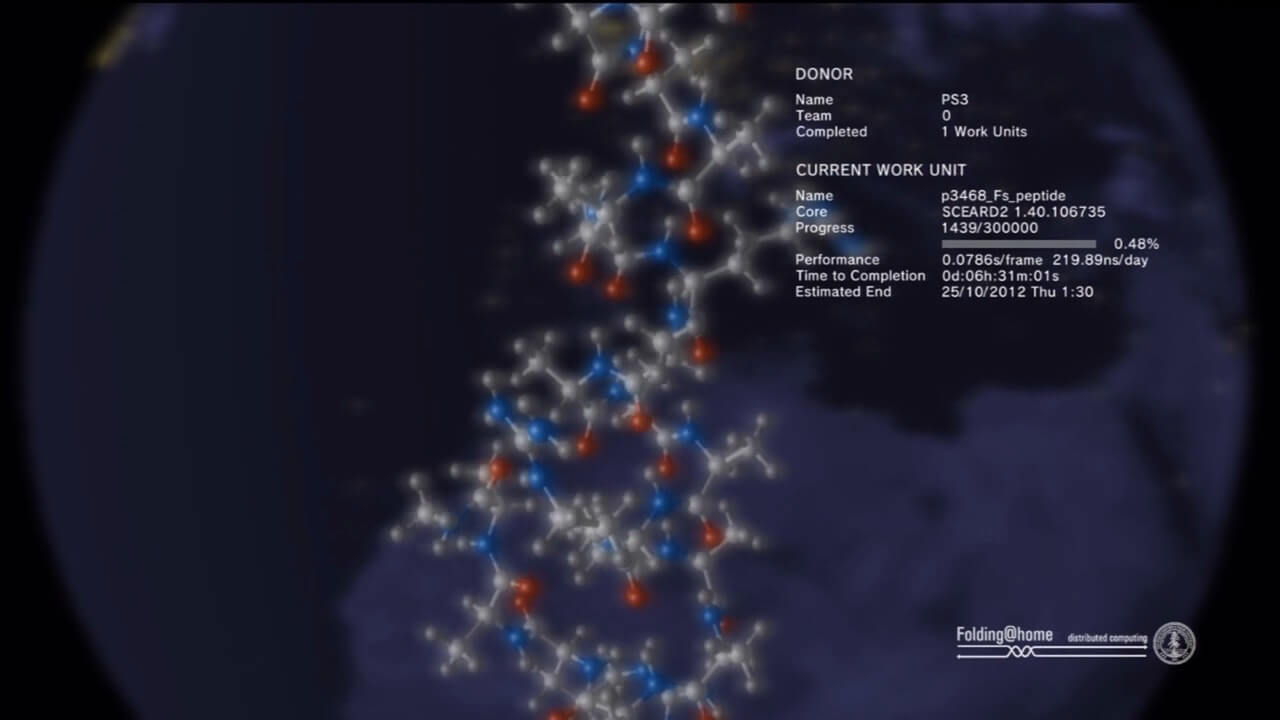

Então, o foco se voltou para a computação distribuída [5]. Em outras palavras, por que se preocupar em aumentar o desempenho de uma única máquina quando você poderia ter várias máquinas menores distribuindo sua carga de trabalho? Por outro lado, essa abordagem não era nova, considerando que todos os consoles analisados neste site contêm mais de um processador. No entanto, foi o desenvolvimento de um “único processador com múltiplos núcleos” que abriu novas oportunidades para o projeto de CPU (que não estavam necessariamente limitadas ao mercado de consoles).

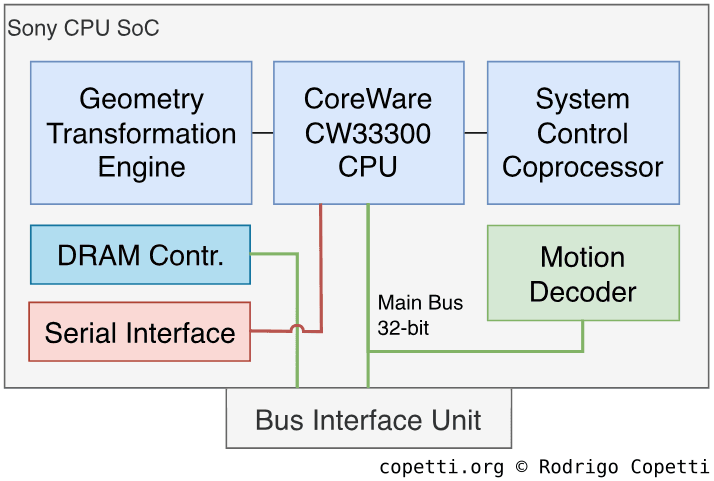

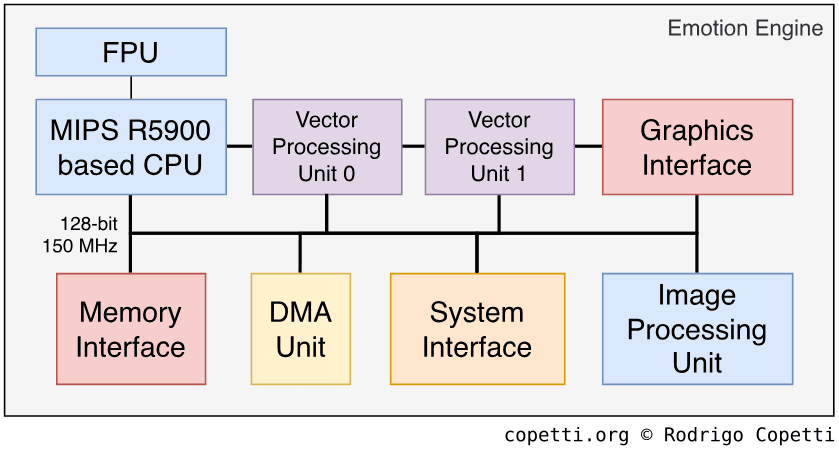

Consequentemente, o Cell fez parte dessa nova onda de pesquisa e desenvolvimento. Essa nova CPU combinou um projeto multi-núcleo com um foco especial no processamento de vetores. Lembre que o processamento de vetores é ótimo para simulações (física, iluminação, etc.) e foi anteriormente materializado na forma do Geometry Transformation Engine e do Vector Units, em seguida você verá por que o projeto do Cell foi um grande avanço em relação aos dois anteriores.

A nova era dos multinúcleos

Este está sendo a arquitetura predominante de muitos consoles poderosos até os dias atuais.

Cada núcleo pode realizar as mesmas tarefas como antes, mas não necessariamente está restrito a essa tarefa.

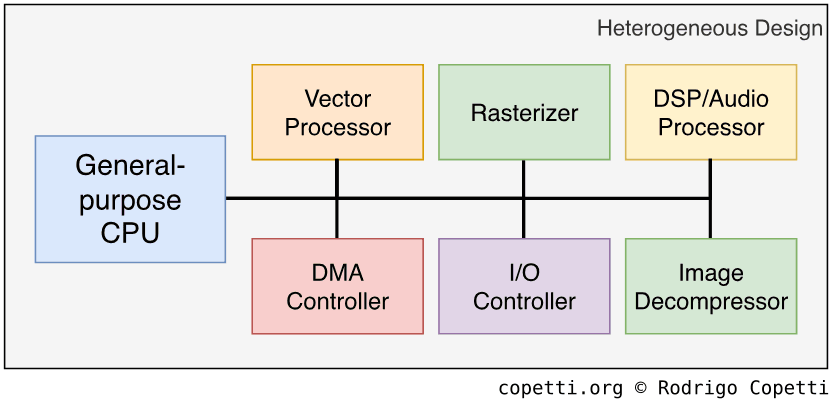

Se você parar para pensar, tanto o processador do PS1 quanto o Emotion Engine já eram processadores multinúcleos. Então, por que houve tanta empolgação em relação ao Cell? Bem, os dois processadores anteriores eram compostos por um núcleo de propósito geral e vários núcleos de aplicação específica (ou seja, processador de áudio, descompressão de imagem, etc.), misturando diferentes arquiteturas, em que o núcleo de propósito geral é responsável por comandar os outros.

Esse tipo de projeto de CPU é chamado de computação heterogênea e era a escolha padrão para construir máquinas especializadas para um conjunto específico de aplicações (jogos, neste caso). Sua contraparte, a computação homogênea, é mais predominante no mercado de PC, onde as CPUs são exigidas a realizar uma ampla gama de tarefas (e todas elas têm a mesma prioridade). Portanto, o último tipo pode ter vários núcleos, mas do mesmo tipo.

Voltando ao assunto, o Cell combina ambos os modelos: há dois tipos de núcleos nesta CPU, um “líder” de propósito geral e oito “assistentes” vetoriais. Esses núcleos vetoriais podem desempenhar vários papéis e, ao fazê-lo, eles cumprem tarefas anteriores que foram originalmente resolvidas por projetos heterogêneos, mas como os vetores do Cell não estão limitados a um único tipo de tarefa, seus núcleos fornecem a flexibilidade dos computadores homogêneos. Resumindo, esse projeto não era perfeito e apresentava algumas limitações, mas ao longo deste texto, você verá os diferentes problemas que o Cell tentou resolver e como ele conseguiu fazê-lo.

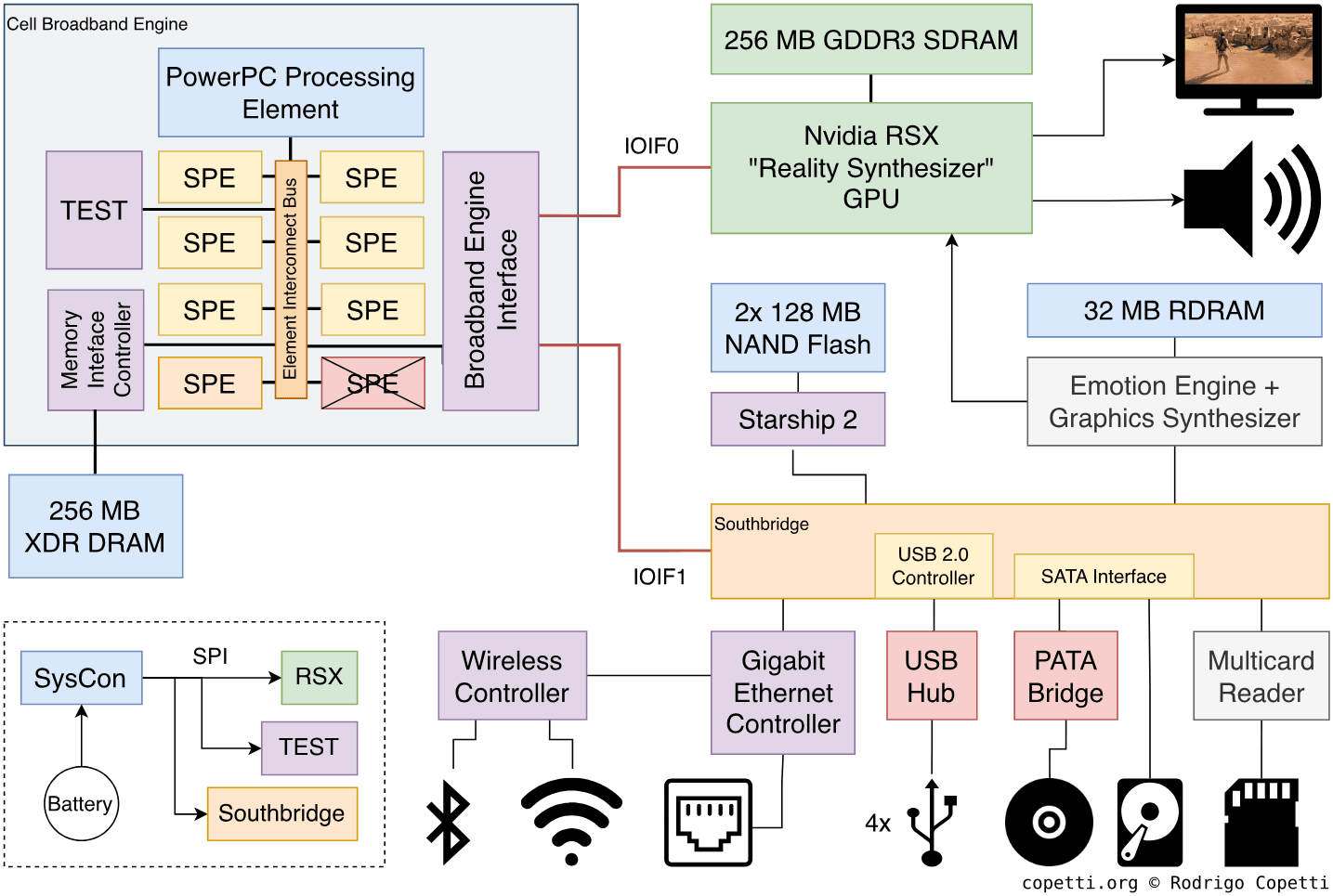

Um olhar sobre o Cell

Após ter explicado toda essa história e teoria, acredito que estamos prontos para apresentar o protagonista desta seção. Este é Cell [6]…

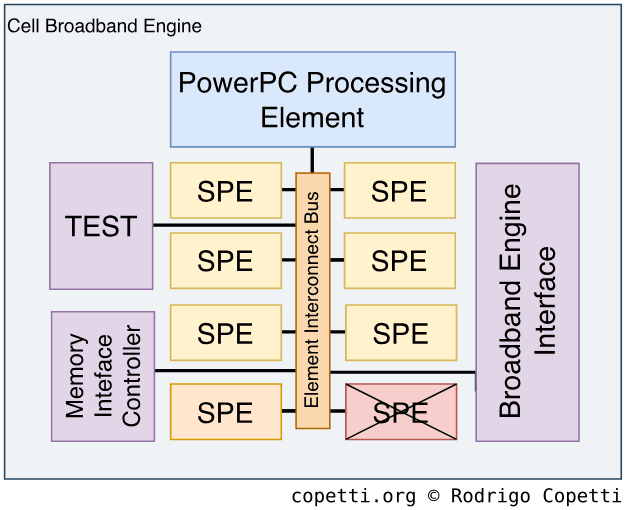

Projetado pela IBM para supercomputação e simulação científica. O “SPE” riscado significa que está desabilitado (inutilizado). O outro “SPE” à esquerda é reservado para o sistema operacional.

… e ao final desta seção, você saberá o que cada componente faz.

Estrutura

O Cell funciona a uma impressionante velocidade de 3,2 GHz e é composto por uma infinidade de componentes. Portanto, para fins de análise, essa CPU pode ser dividida em três áreas principais [7]:

- O líder: esta é a parte do Cell que controla os outros do circuitos. Aqui encontramos um componente chamado PowerPC Processing Element (PPE).

- Os assistentes: esses são tão cruciais quanto o PPE, mas suas capacidades se limitam a um papel de assistente/acelerador. Esse grupo é composto por oito Synergistic Processing Elements (SPEs).

- As interfaces: à medida que a necessidade de largura de banda aumenta exponencialmente, novas interfaces são implementadas para transferir os dados sem produzir gargalos. No grupo de interfaces, encontramos um punhado de protocolos: o Element Interconnect Bus (EIB), o Broadband Engine Interface Unit (BEI), o Memory Interface Controller (MIC) e o Flex I/O buses.

Essas informações serão revisitadas ao longo deste texto com mais detalhes, para que você não precise memorizar esses nomes. O objetivo principal desta seção é permitir que o leitor tenha uma imagem mental da natureza do Cell e se familiarize com todos os componentes que discutiremos no devido tempo.

Como este estudo está organizado

Considerando a estrutura anterior, precisei organizar esta parte do texto para que você não fique sobrecarregado com muitas informações. Assim, começamos a analisar o Cell pelo estudo de cada componente nesta ordem:

- O barramento que conecta todos os componentes, o Element Interconnect Bus (EIB).

- O PowerPC Processing Element (PPE) e seu elemento principal, a PowerPC Processing Unit (PPU).

- Qual é a memória de propósito geral disponibilizada no console.

- Os Synergistic Processing Elements (SPE) e seu elemento principal, a Synergistic Processing Unit (SPU).

- O modelo de programação desenvolvido para programar o Cell de maneira eficiente.

Dito isso, vamos começar a análise real.

Dentro do Cell: o coração

Desde o seu anúncio, o Cell tem sido referido como uma Network-on-Chip (NoC) [8] em vez da definição tradicional do System-on-Chip (SoC), isso se deve ao barramento de dados incomum do Cell, o Element Interconnect Bus (EIB). Já vimos até agora o quão exigentes os componentes da CPU podem ser, além de quão suscetível um sistema é a gargalos. Bem, para enfrentar isso pela décima primeira vez, a IBM criou um novo projeto… e o documentou usando termos análogos à condução de veículos.

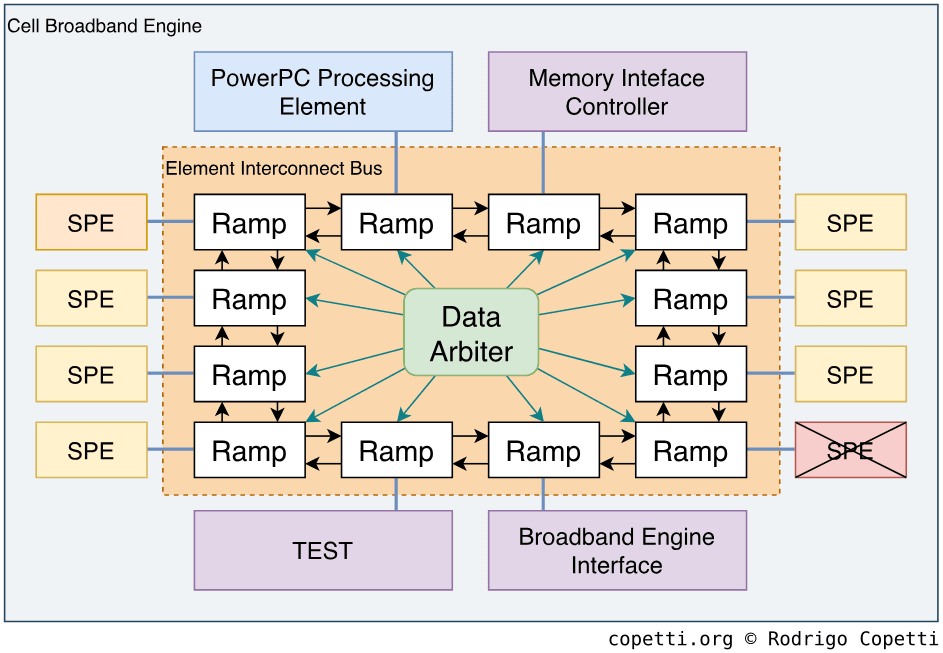

Cada seta entre as “Ramps” (nós) representa dois barramentos unidirecionais, assim, cada nó está conectado ao próximo usando quatro canais.

O EIB é composto por doze nós chamados de Ramps, cada um conectando um componente do Cell. Os Ramps são interconectados usando quatro barramentos, dois deles seguem no sentido horário e os outros dois no sentido anti-horário. Cada barramento (ou canal) possui uma largura de banda de 128 bits. Em vez de usar topologias de barramento único (como o Emotion Engine e seu antecessor fazia), os Ramps são interconectados seguindo a topologia em anel (token ring), onde os pacotes de dados devem passar por todos os vizinhos até chegar ao destino (não há caminho direto). Considerando que o EIB fornece quatro canais, existem quatro rotas possíveis (anéis).

Agora, você pode se perguntar, qual o motivo do uso da topologia em anel se os dados podem acabar viajando por caminhos mais longos (em comparação com um barramento único direto)? Bem, um barramento único é altamente suscetível a congestionamento. Portanto, os engenheiros do EIB decidiram por essa topologia para lidar com grandes quantidades de tráfego concorrente (continue lendo se quiser saber como a topologia em anel ajudou).

Os dados são transferidos na forma de pacotes de 128 bits [9]. Cada anel pode transportar até três transferências simultâneas, desde que os pacotes não se sobreponham. O EIB opera com o uso de créditos de comando, ou seja, sempre que um componente precisa iniciar uma transferência, ele envia uma solicitação ao Data Arbiter (árbitro de dados, em tradução livre) do EIB, que gerencia o tráfego nos anéis. No momento em que a solicitação é aprovada, os pacotes entram no anel e recebem um “token”, que o Data Arbiter usa como metadados para supervisionar a transferência. Além disso, alguns componentes têm prioridade preferencial sobre outros, como o componente Memory Interface Controller (MIC), onde a RAM principal está localizada. Finalmente, o Data Arbiter nunca colocará pacotes em anéis cujo caminho é maior que a metade do anel.

Cada Ramp desempenha um papel na transferência, eles leem o endereço de destino do pacote para saber se devem enviar dados para seu respectivo componente ou encaminhá-lo para o próximo Ramp. Durante cada ciclo de clock, os Ramps podem receber e enviar pacotes de 128 bits (16 bytes) simultaneamente. Portanto, considerando que existem quatro canais e o EIB opera a 1,6 GHz (metade da velocidade do Cell), a taxa máxima teórica de transferência é de 16 bytes x 2 transferências/clock x 4 anéis x 1,6 GHz = 204,8 GB/s, esse valor é, claro, muito otimista e há vários fatores externos (por exemplo, caminho de origem/destino, estado do barramento, etc.) que condicionam o desempenho. De qualquer maneira, muitos trabalhos de pesquisa feitos pela IBM e outros autores compilaram velocidades mais realistas usando experimentos práticos [10].

Agora que você viu como cada componente do Cell está interconectado, é hora de conferir o primeiro componente deste chip…

Dentro do Cell: o líder

Aqui vamos dar uma olhada na “parte principal” do Cell. Essa é a parte do silício encarregada de comandar o resto. O nome do componente é PowerPC Processing Element (PPE) e você pode pensar nele como o MIPS R5900 do Emotion Engine.

Composição do PPE

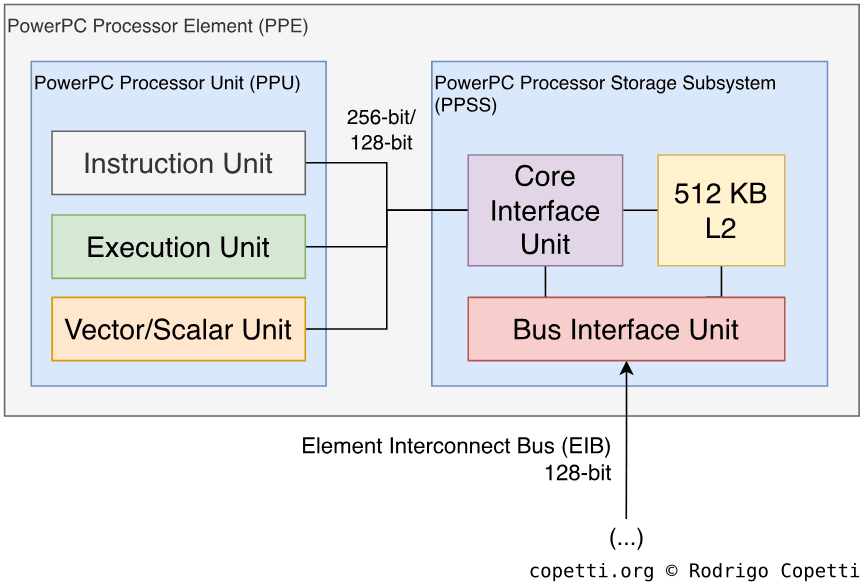

Lembra como eu dividi o Cell em diferentes áreas? Bem, o mesmo pode ser feito com o PPE. A IBM usa o termo “elemento” para descrever a máquina independente [11], mas uma vez dentro dele, usa o termo “unidade” para separar a parte do circuito principal das interfaces que se comunicam com o resto do Cell.

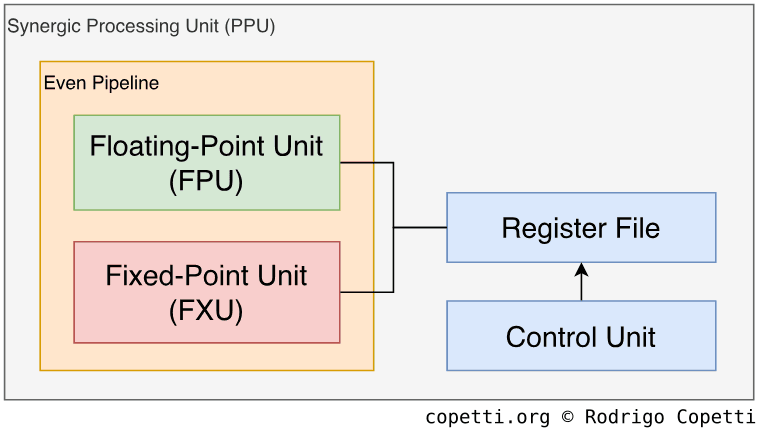

Dito isso, o elemento PowerPC Processor é surpreendentemente composto por duas partes:

- PowerPC Processing Unit (PPU): essa é a parte lógica do PPE (o “núcleo”). Não esqueça que este não é o PPU da Nintendo! (mesmo que compartilhem as mesmas letras do alfabeto latino… na mesma ordem…).

- PowerPC Processor Storage Subsystem (PPSS): a grande interface que conecta a PPU ao mundo externo. Além disso, ela fornece incríveis 512 KB de cache L2.

Como você pode ver, o projeto do PPE (e do restante do Cell) é bastante modular, o que segue os ensinamentos do projeto RISC. Logo você verá que a modularidade é aplicada até mesmo dentro da PPU.

A PowerPC Processing Unit

Vamos dar uma olhada no interior da PPU agora. Para recapitular, mergulhamos no Cell, depois no PPE e, finalmente, na PPU. Vamos analisar a PPU como qualquer outro núcleo de CPU.

Uma arquitetura familiar

Para começar, a PPU não é construída do zero, mas reutiliza a tecnologia PowerPC existente. No entanto, ao contrário de iterações anteriores em que a IBM pegou um processador existente e o atualizou pela metade para atender novos requisitos, o PPE não sucede nenhum projeto anterior de CPU. Em vez disso, a IBM construiu uma nova CPU que segue a versão 2.02 da especificação PowerPC (que acontece de ser a última especificação PowerPC antes de ser renomeada para “Power ISA”). Resumindo, você não encontrará o mesmo projeto da PPU em nenhum chip existente daquela época, no entanto, ele é programado usando o mesmo código de máquina que em outros chips PowerPC.

Dito isto, por que a IBM escolheu a tecnologia PowerPC para desenvolver um chip de alto desempenho? Simples, o PowerPC é uma plataforma madura [12] que desfrutou de cerca de 10 anos de testes e revisões por parte dos usuários do Macintosh testando e revisando, atende a todas as necessidades da Sony e, se surgir a necessidade, pode ser adaptado a diferentes ambientes. Por último, mas não menos importante, o uso de uma arquitetura conhecida é uma boa notícia para compiladores e conjuntos de códigos existentes, o que, para um novo console, é uma grande vantagem inicial.

Vale ressaltar que a IBM foi uma das autoras dos primeiros chips PowerPC, juntamente com a Motorola e a Apple (lembre da aliança AIM). Seja como for, no início dos anos 2000, os chamados membros da aliança já estavam trabalhando separadamente, onde a Motorola/Freescale desenvolveu uma série diferente de PowerPC da IBM.

Recursos distintos

A PPU compartilha parte da história com o PowerPC 970 (chamado de G5 pela Apple), ambos são descendentes do POWER4, um antecessor do PowerPC usado principalmente em estações de trabalho e supercomputadores. Isso fica mais evidente quando eu lhe mostrar as unidades de execução modularizadas. Esta foi uma mudança radical comparado com a CPU da linha 750 do GameCube, que teve uma considerável contribuição da Motorola, mas foi ligeiramente modificada pela IBM.

Voltando ao assunto, a PPU é um processador completo de 64 bits. Isso significa:

- O tamanho de uma palavra é de 64 bits.

- Existem registradores de propósito geral de 64 bits (para ser exato, 32).

- O barramento de dados tem pelo menos 64 bits de largura de banda: nas próximas seções do artigo, você verá que é muito mais amplo do que isso, mas por enquanto, tenha em mente que transferir palavras de 64 bits não penaliza o desempenho.

- O barramento de endereço tem 64 bits de largura: na teoria, a CPU pode acessar até 16 exabytes de memória. Agora, na prática, isso é muito caro se a máquina não abrigar toda essa memória. Então, as CPUs modernas delegam o endereçamento à unidade de gerência de memória (MMU, do inglês * Memory Management Unit*) para fornecer mais usos ao barramento de endereço.

Finalmente, a PPU implementa a ISA PowerPC versão 2.02, incluindo instruções opcionais para raíz quadrada de ponto flutuante [13]. Também foi estendido com um grupo de instruções SIMD chamadas de Vector/SIMD Multimedia Extension (VMX). Por outro lado, alguns elementos estão faltando na especificação original, como o modo little-endian (na verdade, o Cell opera apenas em big-endian) além de algumas poucas instruções.

Os blocos de construção da PPU

Ao aplicarmos uma visão “microscópica” à PPU, podemos observar que esta unidade é composta por diferentes blocos ou sub-unidades que realizam operações independentes (carregar valores da memória, realizar operações aritméticas, etc). As capacidades da PPU são definidas pelo que cada bloco pode fazer e como:

Instruções

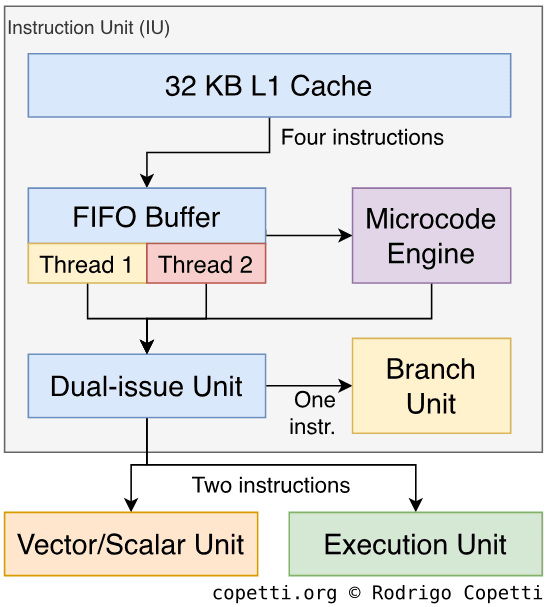

O primeiro bloco é chamado de Instruction Unit (IU) e, como o nome sugere, ele retira as instruções da cache L2 e sinaliza outras unidades para executar a operação solicitada. Assim como seus contemporâneos i686, parte do conjunto de instruções é interpretada com o uso de microcódigo (a IU incorpora uma pequena ROM para esse fim). Por fim, a IU também possui 32 KB de cache L1 para instruções.

A emissão de instruções é realizada com um pipeline de 12 estágios, embora, na prática o número total de estágios varie muito dependendo do tipo de instrução. Por exemplo, o bloco de previsão de desvio (branch prediction) pode ignorar boa parte do pipeline. Se combinarmos a IU com as unidades vizinhas, o número final de estágios geralmente fica próximo de 24 (sim, é um número grande, mas lembre-se que o Cell funciona a 3,2 GHz).

Agora para as partes interessantes, a IU é de dupla emissão: em alguns casos, a IU emitirá até duas instruções ao mesmo tempo, aumentando assim consideravelmente a taxa de transferência. Na prática, no entanto, existem muitas condições para que isso funcione, portanto, os programadores/compiladores são responsáveis por otimizar suas rotinas para que sua sequência de instruções possa aproveitar essa funcionalidade. A propósito, a emissão dupla também foi implementada por outras CPUs, e o termo varia entre os fornecedores, então aqui usei a definição da IBM.

Além disso, para completar, a IU também é multi-threaded, onde a unidade pode executar duas sequências diferentes de instruções (chamadas de “threads”) simultaneamente. Nos bastidores, a IU simplesmente alterna entre os dois threads a cada ciclo, dando a aparência de multi-threading. Essa técnica é historicamente conhecida como Simultaneous Multi-Threading (SMT) ou hyper-threading, como a Intel posteriormente chamou. No entanto, o multi-threading da IBM mitiga efeitos indesejados como bloqueios de pipeline, uma vez que a CPU não ficará mais bloqueada se uma instrução travar o fluxo. Para realizar o multi-threading, os engenheiros da IBM duplicaram os recursos internos da IU, que incluem registradores de propósito geral (anteriormente eu disse que existem 32 registradores disponíveis, isso é por thread. De fato, existem 64 no total!), no entanto, recursos que não pertencem à especificação do PowerPC (como cache L1 e L2; e as interfaces) ainda são compartilhados. Assim, o último grupo é de thread único.

Resumindo, combinando o threading duplo com a emissão dupla, a PPU pode executar até quatro instruções por ciclo. Mesmo que este seja um “cenário ideal”, ele ainda oferece oportunidades de otimização que os usuários eventualmente perceberão na taxa de quadros do jogo!

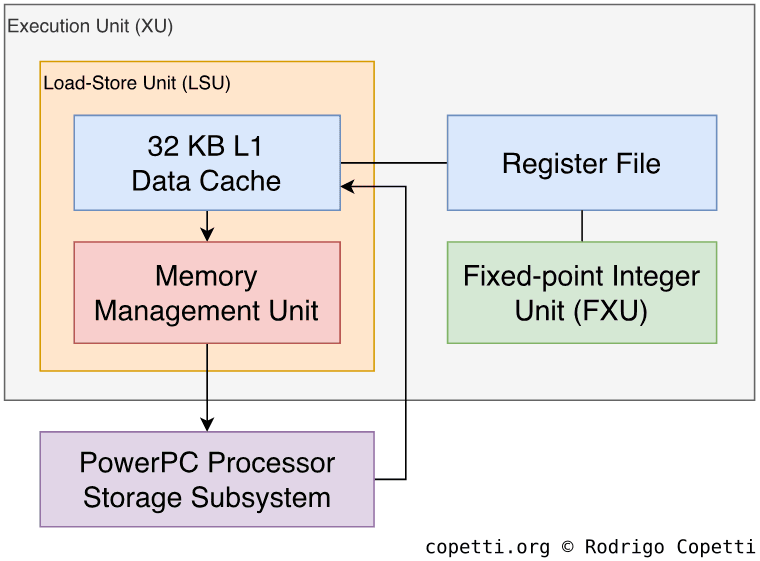

Gerência de memória

Os blocos seguintes concedem à PPU a capacidade de executar instruções de carga-armazenamento e de realizar gerenciamento de memória.

Para começar, a Load and Store Unit (LSU) executa instruções de “carga” e “armazenamento” com suporte de 32 KB de cache de dados L1. Como consequência, essa unidade tem acesso direto à memória e aos registradores.

Além disso, a LSU é acoplada à Memory Management Unit (MMU — Unidade de Gerência de Memória, em tradução livre), o que é uma ocorrência comum no hardware atual. Resumindo, a MMU lida com o endereçamento de memória usando um mapa de endereços virtuais combinados com proteção de memória. Para melhorar este último aspecto, esta MMU em particular apresenta uma unidade de segmentação, que agrupa endereços de memória usando faixas de endereço chamadas “segmentos”. Agora, para evitar degradação de desempenho no processo, um Translation Lookaside Buffer (TLB) (caches de endereços traduzidos) e um Segment Lookaside Buffer (SLB) (caches de segmentos) estão incluídos.

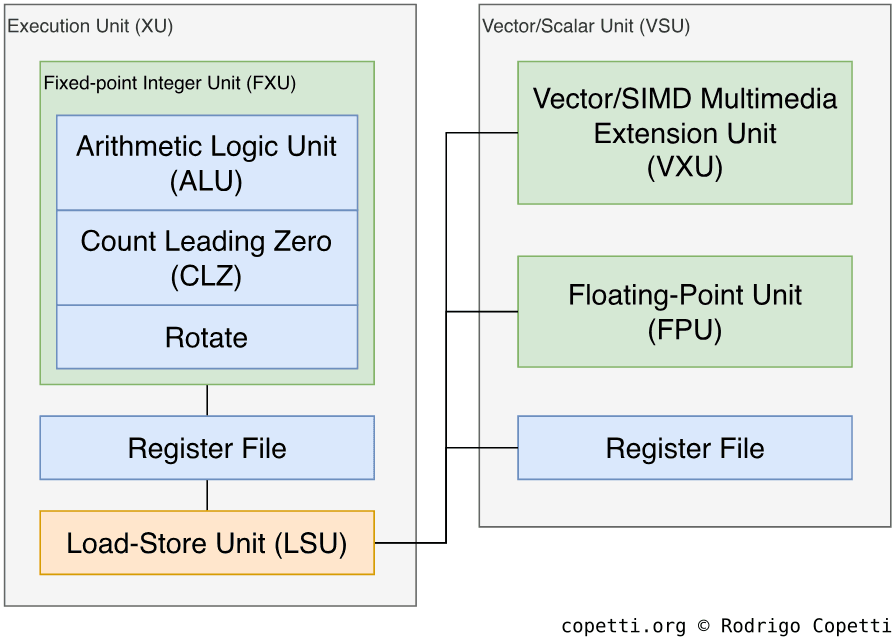

Aritmética

Restam apenas duas unidades do PPU para explicar, aquelas que calculam a matemática que qualquer jogo precisa.

A primeira é uma Fixed-Point Integer Unit (FXU — Unidade de Ponto Fixo, em tradução livre) tradicional. Ela realiza aritmética de inteiros, como divisão, multiplicação, rotação de bits (similar ao deslocamento de bits, mas os bits descartados são retornados para a outra extremidade) e contagem de zeros à esquerda (útil para normalizar coordenadas de vértices, por exemplo). Seu pipeline possui 11 estágios.

Se você olhar o diagrama, verá que a FXU, LSU e MMU são agrupados em uma única unidade chamada de Execution Unit (XU), isso porque eles compartilham o mesmo arquivo de registro.

A segunda unidade é muito mais interessante, a Vector/Scalar Unit (VSU) realiza operações com números de ponto flutuante e vetores. Ela é composta por uma FPU de 64 bits (segue o padrão IEEE 754) e uma Vector/SIMD Multimedia Extension Unit (VXU), que executa um conjunto de instruções SIMD chamado VMX. Este último opera com vetores de 128 bits, compostos por dezesseis valores de 8 bits até quatro de 32 bits [14]. Você pode ter ouvido falar dessa extensão antes, já que “VMX” é o nome da IBM para “AltiVec” da Motorola ou “Velocity Engine” da Apple (viva as marcas registradas). Por outro lado, as capacidades competitivas SIMD do Cell são encontradas em outro processador, então não relaxe ainda!

Concluindo o PPE

Você acabou de ver como o PPE funciona e do que ele é feito, mas o que isso significa para um desenvolvedor?

Afinal, o PowerPC Processing Element é apenas um processador de propósito geral, mas aqui está a questão: ele não é destinado a trabalhar sozinho. Lembre-se do amplo barramento principal (o EIB)? A IBM projetou o PPE para que os engenheiros pudessem combiná-lo com outros processadores para acelerar aplicativos específicos (ou seja, HPC, gráficos 3D, segurança, simulações científicas, rede, processamento de vídeo, etc.) e, como este texto é sobre o PlayStation 3, o restante do Cell é tratado tendo em mente gráficos de computador e física, então este texto reflete esse propósito.

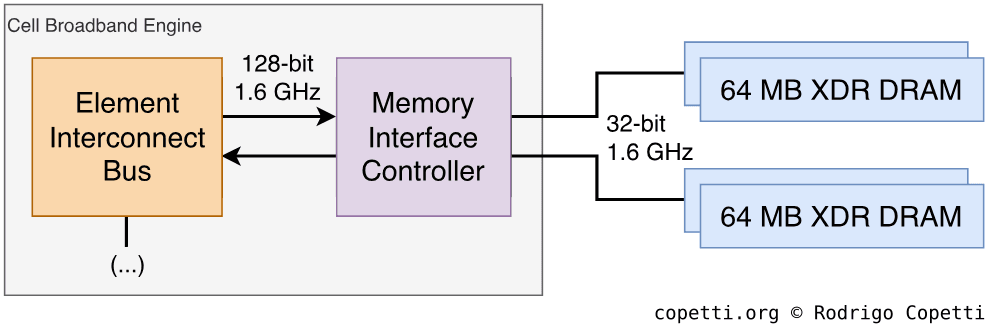

Fora do Cell: a memória principal

Vamos sair um pouco do Cell, pois não importa quão bom seja o PPE se não tivermos um espaço de trabalho adequado (memória) para colocá-lo em funcionamento.

Por isso, a Sony equipou a placa-mãe com 256 MB de XDR DRAM… Mas, novamente, o que isso significa? Para responder a essa pergunta, precisamos dar uma olhada em como funcionam os blocos de memória e como eles se conectam ao Cell.

Primeiramente, o tipo de memória utilizada é chamado de Extreme Data Rate (XDR). Você pode reconhecer a XDR DRAM como sucessora da problemática RDRAM encontrada no Nintendo 64 e no PlayStation 2. Mas não tire conclusões precipitadas ainda!

A Rambus, como qualquer outra empresa, melhora suas invenções. Sua terceira revisão (XDR) opera em taxa óctupla (octa-rate — quatro vezes a taxa de sua adversária, a DDR DRAM) [15]. A latência não é mais um problema, se olharmos para a ficha técnica de seus fabricantes, a latência do XDR é relatada entre 28 ns e 36 ns [16], quase 10 vezes mais rápido do que os chips RDRAM de primeira geração.

A primeira revisão da placa-mãe do PlayStation 3 contém quatro chips de 64 MB, operandos em pares. O XDR é conectado ao Cell usando dois barramentos de 32 bits, um para cada par. Então, sempre que a PPU escreve uma palavra (dados de 64 bits), ela é dividida entre dois chips XDR. Estes últimos são sincronizados em 400 MHz [17].

O Cell se conecta aos chips XDR usando o Memory Interface Controller (MIC), outro componente dentro do Cell (como o PPE). Além disso, o MIC armazena em buffer as transferências de memória para melhorar a largura de banda, mas possui uma grande limitação: o alinhamento de bytes. Em essência, o tamanho mínimo de dados do MIC para transferência é de 128 bytes, o que funciona bem para leituras ou gravações sequenciais. Mas se os dados forem menores que 128 B ou se for exigido a alternância entre gravação e leitura, as penalidades de desempenho aparecem.

Dito isso, o MIC é um gargalo ou um acelerador? Bem, você tem que colocar isso em perspectiva, a otimização de largura de banda é crítica em sistemas que exigem muitos dados. No passado, vimos soluções como write-gather pipe ou o write back buffer, então o MIC é simplesmente uma nova proposta para um problema recorrente. Vale ressaltar que a Sony afirma que a taxa de transferência é de 25,6 GB/s, no entanto, existem muitos fatores que, na prática, condicionam a taxa final (você viu o quão complicado é mover dados de um lugar para outro dentro do Cell).

Isso é tudo para a RAM principal, mas há mais memória em outros lugares: o disco rígido. O PS3 também permite que os jogos usem 2 GB do seu disco rígido interno como uma área de trabalho (similar ao que o Xbox original oferecia) [18].

Dentro do Cell: os assistentes

Já vimos antes como a Sony sempre fornece um processador de propósito geral (o PPE, neste caso), acompanhado de aceleradores para alcançar um desempenho de jogo aceitável (os VPUs e IPU no caso do PS2; e o GTE e MDEC com o PS1). Esta é uma prática comum no hardware de consoles de videogame, já que os processadores de propósito geral podem realizar uma ampla gama de tarefas, mas não são especializados em nada. Consoles de jogos exigem apenas um subconjunto de habilidades (física, gráficos e áudio, por exemplo) então os coprocessadores são usados para fornecer a capacidade de processamento necessária para essas tarefas.

[O PPE] é uma versão simplificada para reduzir o consumo de energia. Então, ele não tem a potência que você vê, por exemplo, em um Pentium 4(…) Se você pegar o código que roda hoje no seu processador Intel ou AMD, qualquer que seja sua potência, e recompilá-lo para o Cell, ele vai rodar — talvez você tenha que mudar uma ou duas bibliotecas, mas vai rodar, sem problemas. Mas ele será cerca de 50% a 60% mais lento e então as pessoas dirão “Oh meu Deus! Esse processador Cell é terrível!” Mas isso ocorre porque você está usando apenas uma componente [19].

– Dr. Michael Perrone, gerente do IBM TJ Watson Research Center’s Cell Solutions Department

Os aceleradores incluídos dentro do Cell do PS3 são os Synergistic Processor Element (SPE). O Cell possui oito deles, embora um seja desativado durante a inicialização do console. Isso ocorre porque a fabricação do chip requer uma quantidade excepcional de precisão (o Cell inicialmente usou o processo de fabricação de 90nm) e a máquina não é perfeita. Então, em vez de descartar os circuitos que apresentam defeito (<10%), o Cell inclui um SPE sobressalente. Assim, se um deles apresentar defeito, o chip inteiro não é descartado. Agora, esse SPE sobressalente sempre estará desativado, independentemente de estar funcionando corretamente ou não (a Sony não pode ter dois PS3s diferentes no mercado).

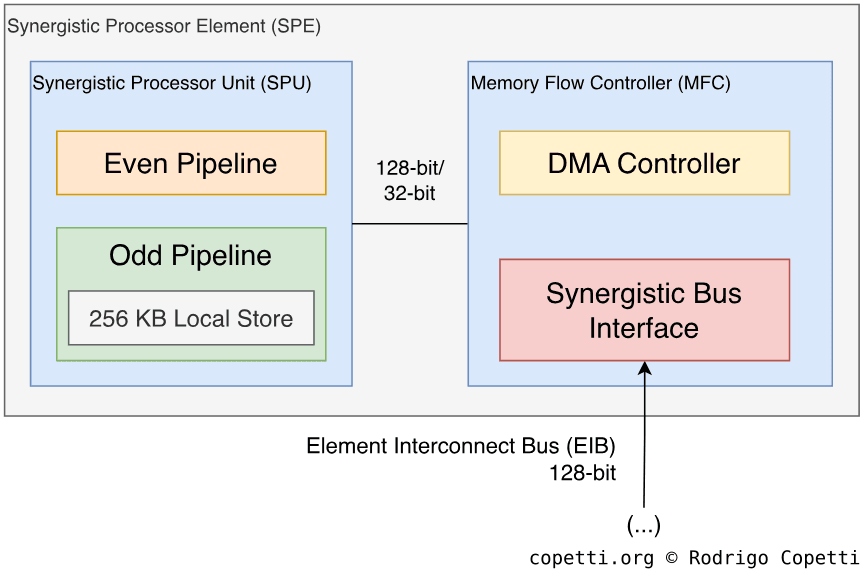

Composição do SPE

Seguindo em frente, o Synergistic Processor Element (SPE) é um pequeno computador independente dentro do Cell e comandado pelo PPE. Lembra do que eu expliquei antes sobre a adoção de elementos de computação homogênea? Bem, esses coprocessadores são um tanto quanto de propósito geral e não restritos a uma única aplicação, então eles serão capazes de auxiliar em uma ampla gama de tarefas, isto é, desde que os desenvolvedores possam programá-los adequadamente.

Assim como fizemos com o PPE, vamos dar uma olhada no SPE. É um tópico mais curto, então se no final você quiser aprender mais sobre os SPEs, confira a seção “Fontes” no final do texto. Dito isso, vamos começar…

O SPE é um processador que segue uma estrutura semelhante à do PPE, sendo composto por duas partes:

O Memory Flow Controller

O Memory Flow Controller (MFC) é um bloco que interconecta o núcleo com o restante do Cell, sendo equivalente ao PowerPC Processor Storage Subsystem (PPSS) no PPE. O trabalho principal do MFC é mover dados entre a memória local da SPU e a memória principal do Cell e manter o SPU em sincronia com seus vizinhos.

Para realizar suas funções, o MFC incorpora um controlador de DMA para lidar com a comunicação entre o barramento EIB e a memória local do SPU. Além disso, o MFC abriga outro componente chamado Synergistic Bus Interface (SBI) que fica entre o barramento EIB e o controlador DMA. É um circuito muito complexo para resumir, mas basicamente interpreta comandos e dados recebidos de fora e envia sinais para as unidades internas do SPE. Como porta de entrada para o Cell, o SBI opera em dois modos: mestre de barramento (onde o SPE é adaptado para solicitar dados de fora) ou escravo de barramento (onde o SPE é configurado para receber ordem de fora).

Como curiosidade, considerando o limite dos pacotes EIB (comprimento de até 128 bits), o bloco de DMA do MFC só pode mover até 16 KB de dados por ciclo, caso contrário, o EIB gera uma exceção de “erro de barramento” durante a execução [20].

A Synergistic Processor Unit

A Synergistic Processor Unit (SPU) é a parte do SPE onde o processador principal reside, equivalente ao “PPU” quando falamos do PPE.

Ao contrário da PPU, a SPU é isolada do restante do Cell. Portanto, não há memória compartilhada entre a PPU ou outras SPUs. Em vez disso, a SPU contém memória local usada como espaço de trabalho. No entanto, o conteúdo da memória local pode ser movido de um lado para outro usando o MFC.

Em termos de funcionalidade, a SPU é muito mais limitada do que a PPU. Por exemplo, a SPU não inclui funções de gerenciamento de memória (tradução de endereços e proteção de memória) ou mesmo funções de última geração (ou seja, previsão dinâmica de desvio). No entanto, ele funciona excepcionalmente bem no processamento vetorial.

Para programar essa unidade, os desenvolvedores usam a PPU para invocar rotinas fornecidas pelo Sistema Operacional do PlayStation 3, que fazem o upload do executável especificamente escrito para a SPU escolhida e a sinaliza para iniciar a execução. Depois, a PPU mantém uma referência à thread da SPU para fins de sincronização [21].

Arquitetura da SPU

Como qualquer CPU, a Synergistic Processor Unit (SPU) é programada usando uma arquitetura de conjunto de instruções (ISA, do inglês Instruction Set Architecture). Tanto a SPU quanto a PPU seguem a metodologia RISC, no entanto, ao contrário da PPU (que implementa uma ISA PowerPC), a ISA da SPU é proprietária e principalmente composta por um conjunto de instruções do tipo SIMD. Como resultado, a SPU apresenta 128 registradores de propósito geral de 128 bits que abrigam vetores feitos de valores de ponto fixo ou de ponto flutuante de 32/16 bits. Por outro lado, para preservar a memória, as instruções da SPU são muito menores, com apenas 32 bits de comprimento. A primeira parte contém o código de operação e o restante pode fazer referência a até três operandos a serem calculados em paralelo.

Isso é muito semelhante antiga Vector Floating Point Unit apresentada no PS2, entretanto muita coisa mudou desde então. Por exemplo, a SPU não exige que os desenvolvedores aprendam uma nova linguagem de montagem proprietária - a IBM e a Sony forneceram kits de desenvolvimento para programar as SPUs usando C++, C ou assembly.

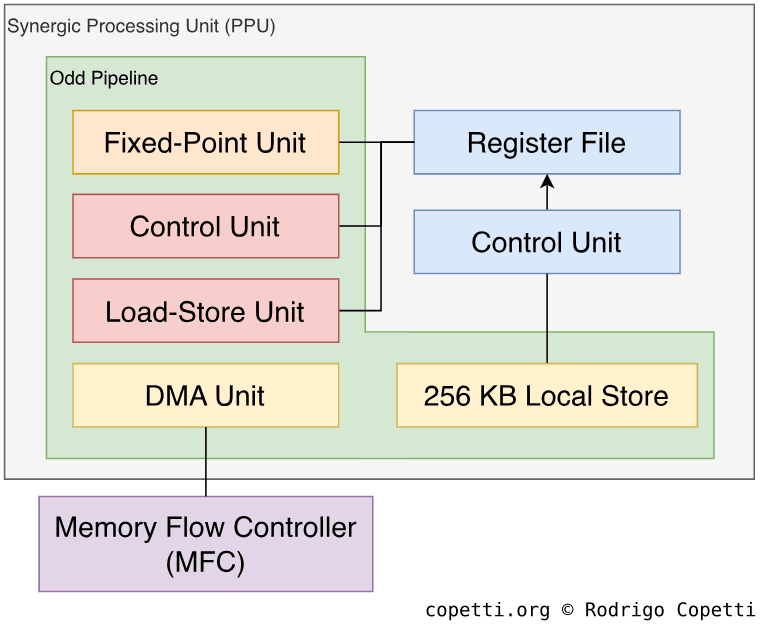

Em termos de projeto, este processador não executa todas as instruções usando a mesma unidade. A execução é dividida em dois blocos ou “pipelines de execução”, uma é chamada de pipeline ímpar e a outra é chamada de pipeline par. Esses dois pipelines executam tipos diferentes de instruções, permitindo que a SPU emita duas instruções por ciclo sempre que possível. Por outro lado, a SPU nunca emitirá duas instruções simultâneas que dependam uma da outra, mitigando assim os riscos de dados (data hazards) que possam surgir.

Vamos dar uma olhada nos dois pipelines [22]:

Pipeline ímpar

O pipeline ímpar executa a maioria das instruções, exceto as aritméticas.

Em primeiro lugar, você encontrará a SPU Load/Store unit (SLS), que faz três coisas essenciais:

- Contém 256 KB de memória local para armazenar instruções e dados. O tipo de memória utilizada é de porta única (considerando que esta é uma área crítica, é um pouco decepcionante que eles não tenham usado chips de porta dupla…). Além disso, o barramento de endereço tem 32 bits de comprimento.

- Executa instruções de carga e armazenamento.

- Encaminha instruções para outro bloco para emissão.

Observe que apenas 256 KB estão disponíveis para armazenar o programa. Considerando que os programas da SPU podem ser compilados usando C/C++, não é fácil prever o tamanho que o arquivo binário terá. Por isso, é recomendando que os desenvolvedores considerem haver apenas metade da memória disponível (128 KB) [23], o que deixa espaço suficiente para o código compilado ocupar o espaço que precisar, embora isso resulte em custo de armazenamento e eficiência.

Finalmente, também há uma SPU Channel and DMA Transport Unit (SSC), que o Memory Flow Controller usa para preencher e/ou buscar memória local, e uma unidade de ponto fixo insignificante que apenas faz embaralhamento e rotação de vetores.

Pipeline par

O * pipeline* par é notável por suas capacidades aritméticas.

Aqui encontramos uma verdadeira Fixed-point Unit (FXU) que realiza aritmética básica, operações lógicas (AND, OR, etc.) e deslocamento de palavras.

Por último, mas não menos importante, temos uma Floating-point Unit (FPU) que realiza operações de precisão simples (float de 32 bits), dupla precisão (double de 64 bits) e inteiro (int de 32 bits). Segue o padrão IEEE com algumas divergências (os pontos flutuantes se comportam de maneira semelhante ao PS2).

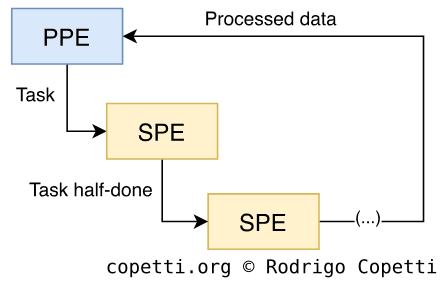

Dentro do Cell: estilos de programação

Como chegamos no final do Cell, você pode se perguntar como os desenvolvedores devem programar esse monstro? Bem, de forma semelhante aos modelos de programação anteriores criados para o Emotion Engine, a IBM propôs as seguintes metodologias [24]:

Abordagens centradas no PPE

As abordagens centradas no PPE são um conjunto de padrões de programação que colocam as principais responsabilidades no PPE e deixam o SPE para a descarga de trabalho. Existem três possíveis padrões:

- Modelo de pipeline multiestágios: o PPE é encarregado de enviar trabalho para um único SPE, que por sua vez realiza os cálculos necessários e passa os resultados para o próximo SPE. Isso continua até que o último SPE na cadeia envie os dados processados de volta ao PPE.

- Por razões óbvias, a IBM não sugere este projeto para tarefas principais, pois requer uma quantidade considerável de largura de banda e tende a ser difícil de manter.

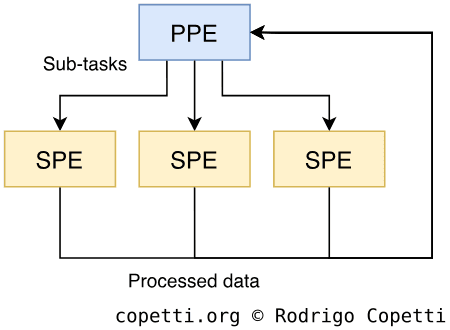

- Modelo de estágios paralelos: o PPE divide sua tarefa principal em subtarefas independentes e envia cada uma para um SPE diferente. Cada SPE retorna os dados processados ao PPE depois de concluídos, e o PPE os combina para produzir o resultado final.

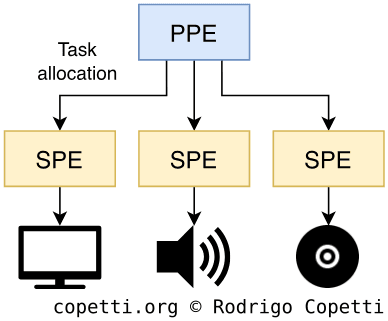

- Modelo de serviços: cada SPE recebe a atribuíção de uma tarefa única (por exemplo, decodificação MPEG, streaming de áudio, projeção de perspectiva, iluminação de vértice, etc.) e o PPE é responsável por enviar dados brutos para o SPE designado. Enquanto espera, o PPE realiza outras funções.

- Embora isso implique que cada SPE terá um único trabalho, sua designação de trabalho não é destinada a durar para sempre. O PPE deve realocar diferentes trabalhos dinamicamente à medida que as necessidades do programa mudam.

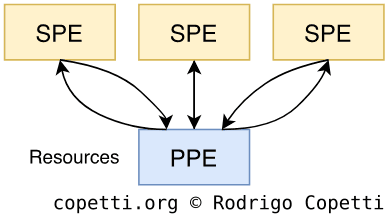

Abordagens centradas no SPE

Em vez de usar os SPEs para servir o PPE, é o contrário. Usando a unidade interna de DMA, os SPEs buscam e executam tarefas armazenadas na memória principal, enquanto o PPE é limitado ao gerenciamento de recursos.

Este modelo é muito mais radical do que o restante, no sentido de que os padrões anteriores estão mais próximos do paradigma “processador geral de propósito com coprocessadores”. Assim, as bases de código que implementam algoritmos centrados no SPE podem ser mais difíceis de portar para outras plataformas.

Conclusão

Como você pode imaginar, embora o projeto multi-núcleos do Cell acelere técnicas emergentes, como geração procedural, nenhum desses projetos é particularmente simples de implementar, especialmente considerando que os estúdios de jogos preferem bases de código que possam ser compartilhadas em diferentes plataformas.

Para dar um exemplo, os desenvolvedores do Unreal Engine 3 (Epic Games) demonstraram as limitações dos SPUs ao tentar implementar seu sistema de detecção de colisão [25]. Seu projeto depende do Binary Space Partitioning (BSP — partição binária do espaço, em tradução livre), um algoritmo fortemente dependente de comparações (branching). Como as SPUs não fornecem previsão dinâmica de desvios como a PPU, sua implementação decepcionou os usuários do PlayStation 3 quando comparada lado a lado com outras plataformas (ou seja, Xbox 360 ou PCs i686, ambas fornecendo técnicas consistentes de previsão em todos os seus núcleos). Assim, a Epic Games teve que recorrer a mais otimizações compatíveis apenas com o Cell.

Suponho que seja apenas uma questão de tempo, paciência e muito aprendizado para que os engenheiros de software aproveitem todo o potencial do Cell. No entanto, a história demonstrou que isso não é viável para todos os estúdios, o que me faz pensar se esse é o motivo pelo qual o hardware do console atual (a partir de 2021) se tornou tão homogêneo.

Gráficos

Se você pensou que o Cell, com todas as suas peculiaridades, poderia cuidar de todas as tarefas do console, então deixe-me dizer algo engraçado: a Sony instalou um chip separado para gráficos 3D.

Parece que mesmo com um chip de supercomputador, a Sony ainda teve que buscar uma GPU para finalizar o PlayStation 3. Isso faz você se perguntar se a IBM/Sony/Tpshiba encontrou algum obstáculo ao tentar escalar ainda mais o Cell, então a Sony não teve outra opção senão buscar ajuda de uma empresa de processadores gráficos.

Nós iniciamos esta equipe ICE [Iniciativa para um Motor Comum] com o objetivo de desenvolver alguma tecnologia central que pudesse ser compartilhada entre todos os primeiros partidos (…) Por um tempo, [PS3 teve] sem GPU, ia rodar tudo com SPUs. A equipe da ICE provou ao Japão que isso era simplesmente impossível. Isso seria ridículo. Em termos de desempenho, seria um desastre. É por isso que eles finalmente adicionaram a GPU, mais perto do fim [26].

– Fontes anônimas da Naughty Dog

O que eu sei é que o PS3 contém um chip GPU fabricado pela Nvidia, destinado a aliviar parte do gráfico. O chip é chamado de Reality Synthesizer ou “RSX” e roda a 500 MHz [27]. Sua frequência de clock parece preocupante quando comparada com a do Cell (3,2 GHz), mas veja que a GPU é melhor equipada para realizar quantidades grandes de operações em paralelo. Portanto, é uma questão de encontrar um equilíbrio entre o Cell e o RSX quando se trata de construir o pipeline gráfico (embora eu deva confessar que isso parece mais simples no papel do que na prática).

Agora, farei a análise do RSX e suas capacidades gráficas no mesmo nível que fiz com o Cell.

Visão geral

Já tinha se passado cinco anos desde que a Nvidia lançou a linha GeForce3/NV30 em 2001, e na época o mercado de processadores gráficos era disputado por empresas fortes como a 3dfx, a S3 e a ArtX/ATI. No entanto, nos anos seguintes, o número dessas empresas reduziu lentamente até o ponto que, em 2006, apenas a ATI e a Nvidia permaneciam como os principais fornecedores de placas de vídeo no mercado de PCs.

O RSX herda a tecnologia existente da Nvidia, é referido como sendo baseado no modelo 7800 GTX vendido para PCs, que implementa a arquitetura GeForce7 (ou NV47) [28], também chamada de “Curie”.

Na minha análise anterior do Xbox, eu falei sobre a GeForce3 e seus estreantes shaders de píxel. Então, o que mudou? Houve altos e baixos, mas principalmente mudanças incrementais, nada muito revolucionário em comparação com os shaders de píxel da GeForce3.

Por outro lado, enquanto o 7800 GTX depende do protocolo PCI Express para se comunicar com a CPU, o RSX foi remodelado para trabalhar com um protocolo proprietário chamado Flex I/O [29], uma interface diferente dentro do Cell projetada para se conectar a chips vizinhos. O Flex I/O opera em dois modos:

- O modo BIC para conectar outros processadores Cell (a ser usado em ambientes com múltiplos processadores).

- O modo IOIF mais lento para conectar até dois periféricos, um “rápido” e um “lento”.

Infelizmente, o RSX não é o Cell, então ele passa pelo protocolo IOIF, usando o slot mais rápido.

Para fins de comparação, o IOIF funciona como um barramento paralelo de 32 bits com uma largura de banda teórica de até 20 GB/s, enquanto o PCI-Express usado no 7800 GTX (x16 1.0) é um barramento serial de 16 bits com uma largura de banda teórica de até 4 GB/s.

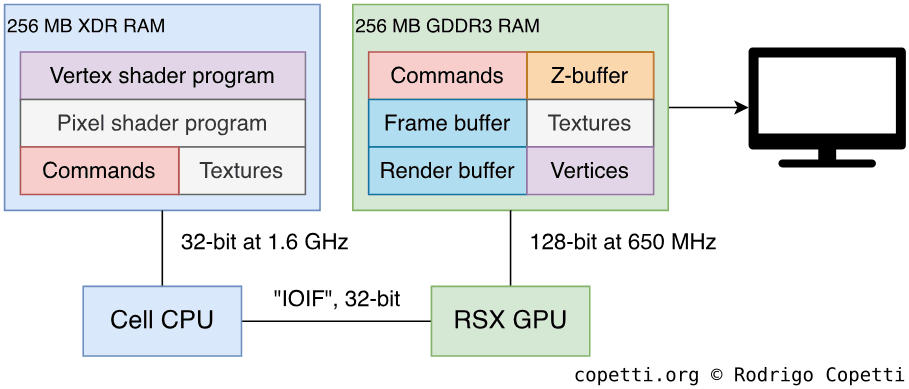

Organizando o conteúdo

O RSX tem 256 MB de GDDR3 SDRAM dedicados à sua disposição. Surpreendentemente, é o mesmo tipo de memória encontrada no Wii. O barramento de memória funciona a 650 MHz com uma largura de banda teórica de até 20,8 GB/s.

Dentro desses 256 MB, o Cell pode colocar tudo o que o RSX precisa para renderizar um quadro. Isso inclui os dados de vértices, os shaders, as texturas e os comandos. Graças ao barramento Flex I/O do Cell, o RSX também pode utilizar os mencionados 256 MB de memória XDR (RAM principal da CPU) como espaço de trabalho, embora isso acarrete algumas penalidades de desempenho. Isso é útil se o quadro renderizado for processado posteriormente por um SPU, por exemplo.

Como pode ser visto, embora o console não tenha implementado uma arquitetura UMA (do inglês, Unified Memory Architecture), ainda é possível distribuir dados gráficos por diferentes chips de memória se os programadores decidirem fazê-lo. Menciono isso porque gostaria que muitos “analistas técnicos” lessem mais sobre esses recursos antes de gritar declarações super resumidas como “O PS3 era limitado porque não tinha arquitetura UMA”. Isso pode ser verdade em certos casos, mas, a menos que mencionem esses recursos, essa afirmação genérica é, na minha opinião, enganosa.

Por fim, o RSX suporta muitas formas de otimização de dados para economizar largura de banda, exemplos incluem compressão de cores 4:1, compressão de profundidade e modo “tiled” (explicarei mais sobre isso mais tarde).

Construindo o quadro (frame)

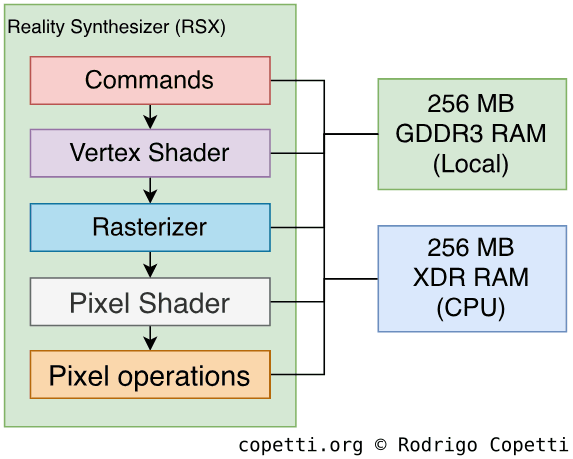

Vamos dar uma olhada em como o RSX processa e renderiza cenas em 3D.

Seu modelo de pipeline é muito semelhante ao da GeForce3, mas foi turbinado com cinco anos de progresso tecnológico. Então, sugiro verificar este artigo [30] antes, já que este texto foca nas novas funcionalidades. Também recomendo ler sobre a GPU do PlayStation Portable, pois muitos dos novos desenvolvimentos e das novas necessidades se sobrepõem com a desse chip. Dito isso, vamos ver o que temos aqui…

Comandos

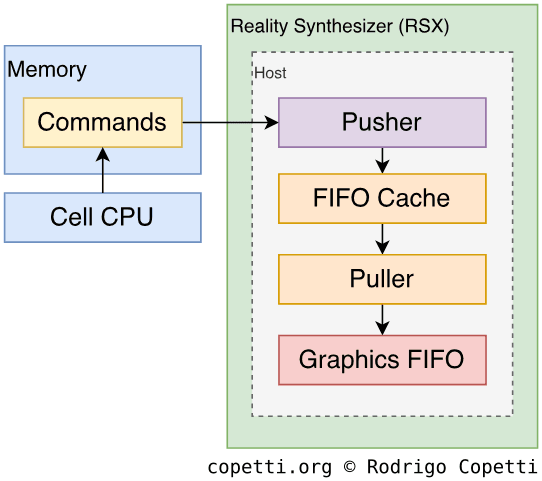

Assim como acontece com qualquer outra GPU, deve haver um bloco de circuito encarregado de receber as ordens de fora. Com o RSX, isso é tratado por dois blocos: Host e Graphics Front End.

O Host é responsável por ler os comandos da memória (seja local ou principal) e traduzi-los em sinais internos que outros componentes do RSX entendam. Isso é feito com o uso de quatro sub-blocos:

- Pusher: busca comandos gráficos da memória e interpreta as instruções de desvio. Ele também contém 1 KB de buffer de pré-busca. Os comandos processados são enviados para uma cache FIFO.

- Cache FIFO: armazena até 512 comandos decodificados pelo Pusher obedecendo à ordem de chegada na cache para fornecer acesso rápido.

- Puller: coleta comandos da cache FIFO sempre que o RSX está pronto para renderizar e os envia para a próxima unidade.

- Graphics FIFO: armazena até oito comandos que serão lidos pelo Graphics Front End.

O Graphics Front End lê do Graphics FIFO e sinaliza para as unidades necessárias dentro do RSX para computar as operações. Caso você lembre, isso é equivalente ao “pfifo” na GeForce3.

Como pode ser visto, comandos e dados passam por muitos buffers e caches antes de chegar ao destino final. Isso é intencional, pois evita que o pipeline fique parado devido as diferentes unidades e barramentos operando em velocidades diferentes. Assim, a memória cache tira aproveito da largura de banda rápida sempre que possível.

Shader de vértice

A próxima unidade é o bloco de Geometry Processing, uma evolução do “Bloco de Vértices” da GeForce3 que realiza a transformações de vértices. Permanece programável com o uso de shaders de vértices, que atualmente é um recurso amplamente utilizado na indústria de gráficos. Além disso, o limite de instruções foi aumentado para um mínimo de 512 instruções (originalmente, 136 era o limite!).

O bloco que executa shaders é chamado de Vertex Processing Engine (VPE) e pode processar um vértice por pulso de clock. Como se não bastasse, há oito VPEs trabalhando em paralelo. Desde a série GeForce6, a Nvidia alinhou sua interface de programação de shader a um modelo chamado “Vertex Shader Model 3” ou “vs_3_0_”, um padrão desenvolvido pela Microsoft para uso com suas bibliotecas DirectX 9.0c [31]. Os VPEs também são compatíveis com o modelo não proprietário OpenGL 2.1 [32] e com a variante da Nvidia (Cg) [33].

Comparado com a GeForce3, temos novas instruções disponíveis para desvios e chamadas de sub-rotina. Além disso, o VPE contém quatro amostradores de textura (texture samplers) que buscam as cores das texturas durante este estágio, caso os programadores queiram usar esta unidade para realizar algumas operações nelas.

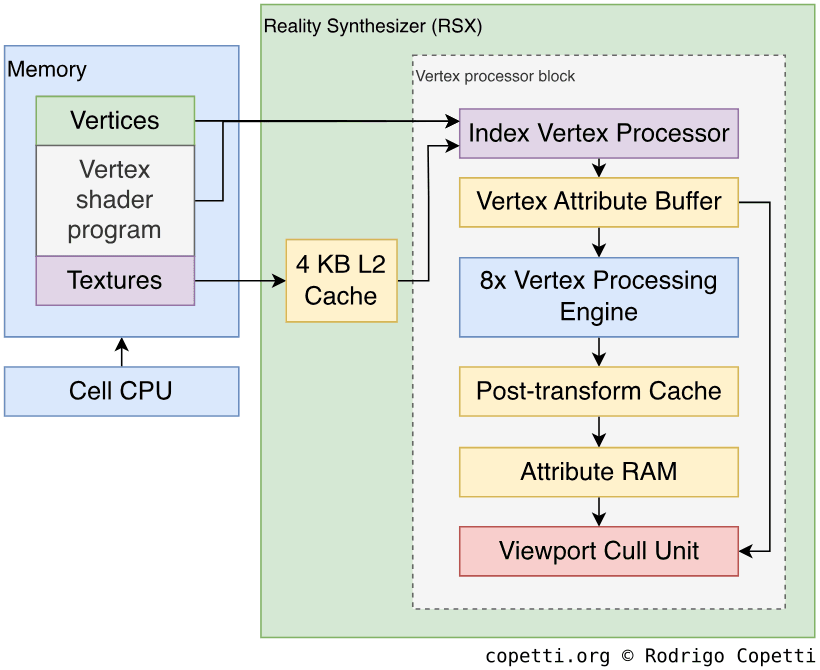

O bloco de Geometry Processing funciona da seguinte maneira:

- O Index Vertex Processor (IDX) busca e armazena na cache de dados de vértices e texturas da VRAM. Em seguida, envia os dados para o VAB.

- O Vertex Attribute Buffer (VAB) busca os dados na cache IDX e os redireciona para cada VPE.

- Cada VPE processa os dados com base no shader carregado. Ele computa uma instrução de shader por pulso de clock.

- O resultado de cada VPE é enviado para o Post Transform Cache, que armazena em cache os resultados para pular cálculos idênticos sobre o mesmo vértice. Isso se aplica se índices de vértices forem usados em vez de dados de vértices.

- O resultado final é armazenado na Viewport Cull Unit (VPC), que aplica corte para descartar vértices encontrados fora da janela de visualização; e na Attribute RAM (ATR), que armazena em cache os atributos dos vértices (textura, cor, neblina, etc.) a serem lidos nas próximas etapas.

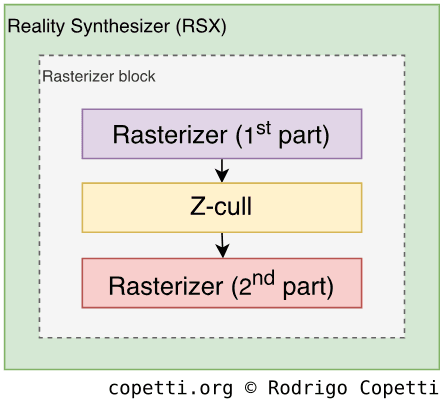

Rasterização

Seguindo, é hora de converter (rasterizar) os vértices em píxeis. O rasterizador do RSX é bastante rápido, ele pode rasterizar até 8x8 píxeis (64) por ciclo e funciona com um buffer de imagem até 4096x4096 píxeis (embora os desenvolvedores possam precisar de menos que isso).

O rasterizador aceita pontos, linhas (incluindo tipos fechados e em tiras), triângulos (incluindo tiras e leques), quadriláteros e polígonos regulares. Naturalmente, como nesta geração de consoles, o rasterizador trabalha com coordenadas de subpixel, onde os pontos de amostragem são meias-coordenadas (0,5) de píxeis. Isso permite que a unidade aplique métodos de anti-serrilhamento, como o multiamostragem (multisampling), posteriormente. A multiamostragem consiste em rasterizar a mesma geometria várias vezes, mas deslocando alguns subpíxeis a cada lote (o RSX suporta quatro modos de deslocamento) e, em seguida, calcular uma média. Isso resulta em uma imagem suavizada.

Além disso, essa unidade também realiza ocultação de profundidade (z-culling) usando a RAM dedicada dentro do RSX (com capacidade de cerca de três milhões de píxeis). Isso economiza o processamento de píxeis e estênceis que já foram renderizados e permite realizar testes de profundidade (z-test) antecipados na geometria que está chegando.

Uma unidade separada é usada para rasterizar objetos 2D (sprites), embora esta seja isolada do pipeline 3D. Consequentemente, o RSX trabalha em dois modos, 2D e 3D, mas alternar entre eles, intermitentemente, é caro em termos de desempenho.

Shader de píxel

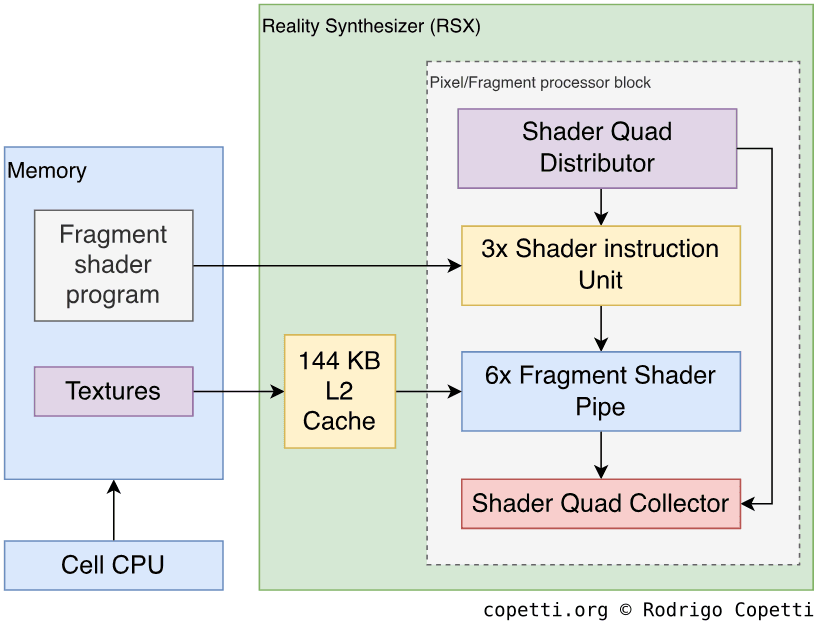

A próxima unidade é o bloco Fragment Shader & Texture, que é uma unidade programável (por meio do uso de “programas de fragmentos” ou “shader”) que aplica mapeamento de texturas e outros efeitos.

Sendo o sucessor avançado das unidades de textura da GeForce3, o novo bloco contém seis unidades de fragmento (também chamadas de “pipes”), cada uma processando 2x2 texels (chamados de “quads”). Para organizar várias unidades trabalhando simultaneamente, outro sub-bloco chamado Shader Quad Distributor (SQD) é colocado para distribuir quads para cada unidade de fragmento. Depois, cada unidade de fragmento carrega o programa de fragmentos.

Para realizar operações, cada pipe contém uma enorme quantidade de 1536 registradores de 128 bits. Além disso, cada pipe pode processar vários quads em paralelo (multithreading), embora o número de quads processados em paralelo dependa do número de registradores alocados para o programa de fragmento (número de threads = 1536 ÷ número de registradores reservados pelo shader). Em termos globais, até 460 quads podem ser processados em paralelo. Além disso, até três pipes de fragmentos podem processar duas instruções em simultâneo (emissão dupla, como a PPU) contanto que as instruções não dependam uma da outra.

As unidades de fragmento fornecem instruções semelhantes em termos aritmeticos à unidade de vértice, com a adição de instruções relacionadas a textura, com vários tipos de busca de textura (uma vez que as texturas podem ser codificadas usando muitas estruturas e, em seguida, comprimidas) e descompactação. Assim como o bloco de vértice, o shader de fragmento segue o modelo shader de píxel 3.0 do DirectX [34], o perfil NV_fragment_program2 do OpenGL [35] e o perfil “fp40” do Cg [36]. Tudo isso para facilitar a programação e evitar aprender APIs de baixo nível desde o início.

Por fim, como as unidades estarão constantemente buscando fragmentos de textura da RAM de vídeo ou da RAM principal, este bloco inclui três caches de textura: 4KB de cache L1 para cada pipe, 48 KB de cache L2 para buscas na RAM de vídeo; e 96 KB de cache L2 para a RAM principal. Observe que a cache da RAM principal é significativamente maior, isso foi uma decisão consciente para compensar a maior latência.

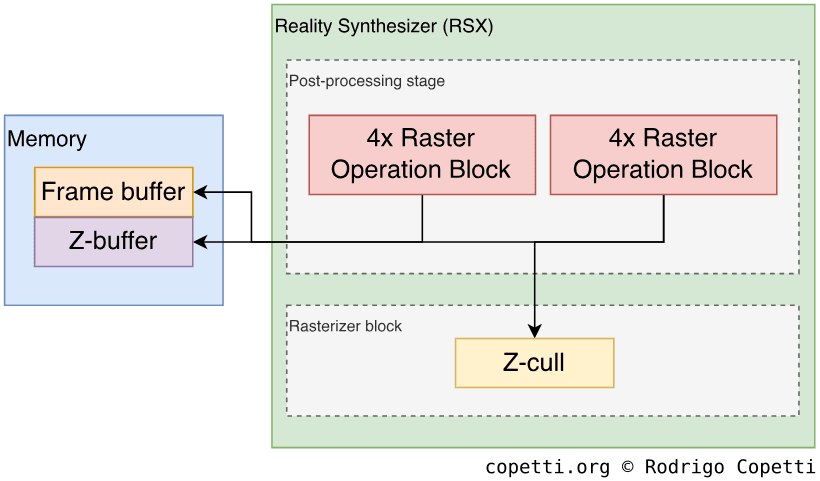

Operações de píxeis

Antes de escrever os resultados no buffer de imagem (armazenado na VRAM ou na RAM principal), um bloco final chamado Raster Operation Block (ROP) realiza testes finais nos píxeis resultantes.

Existem dois conjuntos de ROPs compostos por quatro blocos cada (oito no total). Cada grupo realiza teste de profundidade (z-testing), mistura alfa e a gravação final na memória. No total, este circuito pode processar até 16 valores de profundidade (z-values) e 8 cores de píxel por pulso de clock. Curiosamente, a variante para PC, Nvidia 7800 GTX, apresenta 16 ROPs em vez de 8, talvez esse corte tenha sido feito para priorizar a largura de banda de memória consumida pelas SPUs?

Para economizar ainda mais largura de banda, os ROPs também fornecem compressão de cor e compressão Z (z-compression). Além disso, há um Tiling mode disponível para otimizar o acesso à memória pelo codificador de vídeo. No Tiling mode, o buffer de imagem é armazenado em blocos contínuos de 128 B ordenados da mesma forma que seriam transmitidos/escaneados. Assim, a GPU é poupada de fazer trocas de páginas (usadas para endereçamento de memória) enquanto transmite o buffer de imagem para exibição, melhorando consequentemente a largura de banda. Esses ‘tiles’ são armazenados em locais marcados na memória exclusivos para esse tipo de endereçamento.

Uma saída de vídeo unificada

Foram-se os dias dos conectores de vídeo exclusivos de consoles e dezenas de sinais analógicos espremidos juntos em um único conector para acomodar todas as regiões do planeta. O PlayStation 3 finalmente incorporou um sinal de vídeo unificado que logo foi adotado em todo o mundo: a High Definition Media Interface (HDMI), usada para transferir áudio e vídeo simultaneamente.

O conector HDMI é composto por 19 pinos [37], todos em um único soquete. Ele transfere um sinal digital, o que significa que a imagem e o áudio são transmitidos usando valores discretos de zero e um (e não uma série de valores contínuos encontrados em sinais analógicos). Consequentemente, ele não sofre com interferência ou degradação de imagem que equipamentos anteriores sofriam, como artefatos na tela produzidos por cabos SCART baratos.

Até hoje, o protocolo HDMI é continuamente revisado [38], com novas versões da especificação oferecendo mais recursos (por exemplo, resolução de imagem maior, taxa de atualização, espaço de cores alternativos, etc.) enquanto mantém o mesmo meio físico para compatibilidade com versões anteriores.

Durante o ciclo de vida do PS3, a Sony adicionou certas funcionalidades das novas revisões do HDMI no console por meio de atualizações de software [39]. O último protocolo compatível com o PS3 é a versão 1.4, trazendo suporte para “televisores 3D”, embora outras capacidades, como resoluções de vídeo mais altas, permaneçam limitadas a 1920x1080 píxeis (e mesmo assim, a maioria dos jogos renderizava seu buffer de imagem em 1280x720 píxeis).

Visão/projeção 3D “real”

Mas o que é esse “televisor 3D” que eu mencionei antes? Bem, acontece que a vida útil do console coincidiu com uma febre passageira por TVs 3D (as chamadas 3DTV) [40]]. Para suportá-las, a Sony atualizou seu SDK para ajudar na renderização de quadros estereoscópios na RSX e implementou a “especificação 3D” em seu codificador HDMI. O que acontecia nos bastidores é que o codificador transmitia dois quadros por vez, e a televisão os alternava de maneiras semelhantes ao que os óculos 3D do Master System faziam 30 anos antes.

Áudio

Receio que você não encontrará muitas informações nesta seção, principalmente porque desde o PlayStation Portable, o áudio mudou silenciosamente para o lado do software. Em outras palavras, não existem mais chips de áudio dedicados.

Observe que, enquanto a necessidade de gráficos melhores tende a crescer exponencialmente (os consumidores querem mais cenários, detalhes e cores melhores), não há a mesma demanda por som. Presumo que isso ocorre porque as capacidades técnicas já alcançaram nosso limite cognitivo (taxa de amostragem de 44,1 kHz e resolução de 16 bits). A única coisa que ainda resta é implementar mais canais e efeitos, mas para isso não é necessário tanto poder de processamento a ponto de exigir a instalação de chips dedicados, pelo menos para equipamentos de uso doméstico.

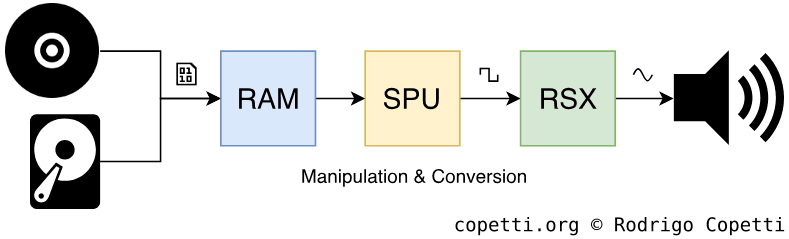

Então, no fim das contas, o áudio agora é completamente implementado com software e processado pelas SPUs (quero dizer pelas Synergistic Processor Units, não pela Sound Processing Unit! É um pouco irônico que ambos compartilhem a mesma sigla…). Continuando, a Sony fornece diversas bibliotecas em seu SDK que instruem as SPUs a realizar sequenciamento, mixagem e transmissão de áudio. E se isso não for suficiente, muitos efeitos também podem ser aplicados.

Dito isso, onde o sinal de áudio é enviado para transmissão? Para o RSX. Esse chip também contém as portas usadas para transmitir sinais de áudio brutos para a TV. Antes de enviar, o sinal é codificado em diferentes formatos, dependendo da saída selecionada (analógica, HDMI ou S/PDIF, este último também é chamado de “áudio digital”).

Entrada/Saída e a retrocompartibilidade.

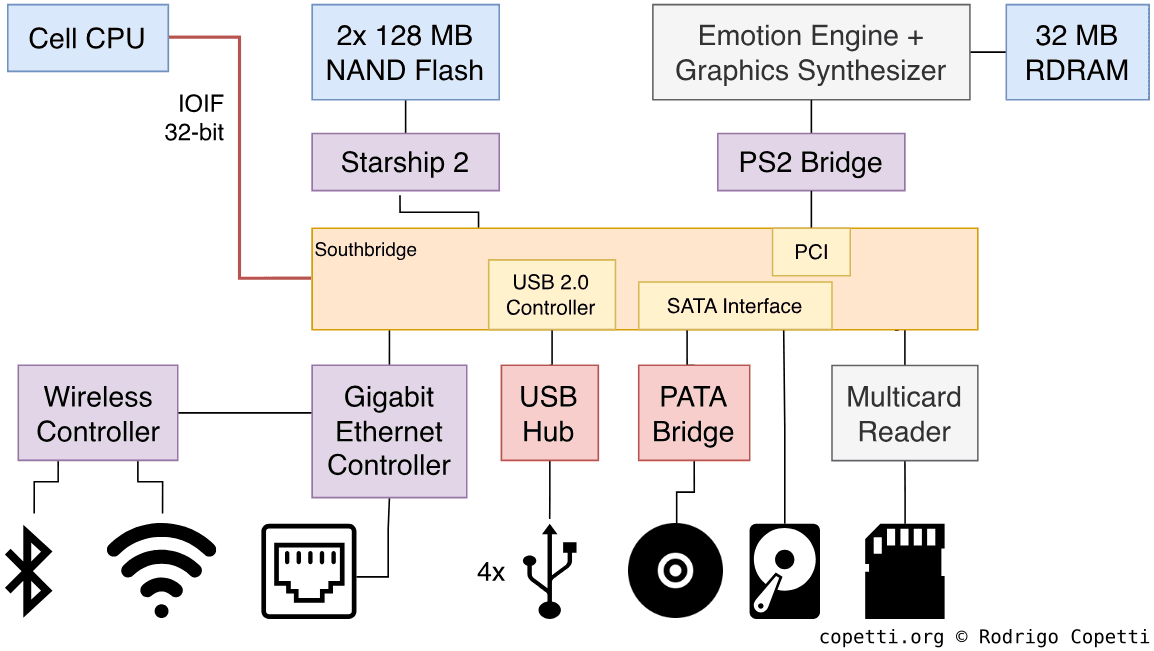

Todas as operações de entrada e saída são delegadas a outro chip robusto chamado Southbridge [41]. Isso é muito semelhante à arquitetura adotada pelo Xbox original lá atrás. Parece que a diferença das arquiteturas dos consoles está se tornando menor, ou talvez essa abordagem tenha se mostrado muito confiável e seja agnóstica em relação à arquitetura, deixarei você decidir.

Assim como no IOP do PS2, o Southbridge é completamente proprietário, embora feita desta vez pela Toshiba (eles a chamaram de “Super Companion Chip” (chip super companheiro, em tradução livre) [42]). Portanto, embora ainda seja um pedaço de silício obscuro, ele faz um trabalho superior em consolidar muitas interfaces e protocolos, tanto externos (ou seja, USB, Ethernet, etc.) quanto internos (ou seja, SATA). Para referência, no passado, a baixa velocidade do clock do IOP acabava causando gargalos nas interfaces rápidas como ATA e Ethernet, reduzindo muito sua largura de banda total.

Além disso, o Southbridge implementa algoritmos de criptografia para proteger a comunicação entre protocolos de maneira transparente, como os dados do disco rígido.

Em geral, o Southbridge incorpora uma quantidade enorme de interfaces, isso se deve ao fato de que o console foi projetado durante a tendência das “centrais multimídia”. Não era suficiente para os consoles de videogame apenas reproduzirem jogos, eles também precisavam se tornar reprodutores de DVD e Blu-ray, decodificadores (parcialmente), visualizadores de fotos (importando as fotos da câmera usando o leitor de cartões múltiplos) e possivelmente realizar mais outras funções a medida que as necessidades evoluiam (graças ao seu sistema oeracional atualizável).

Interfaces externas

Isso era bastante “premium” para um console que custava £425! (£628 em 2021).

Para reduzir ainda mais os custos, modelos posteriores selaram a baía e removeram o leito de cartões e duas portas USB.

No caso das portas acessíveis pelo usuário, o Southbridge está conectada a:

- Um hub USB 2.0: fornece quatro portas frontais USB-A. Estas portas podem ser usadas para acessórios ou para conectar/carregar os controles.

- Uma interface Serial ATA (SATA): conecta a unidade de Blu-ray e um disco rígido de 2,5 polegadas.

- Até 2008, leitores de Blu-ray se conectavam com ATA paralelo (PATA) [43], então um chip intermediário foi instalado para fazer a conversão SATA → PATA.

- Um Controlador Ethernet 1000/100/10 (Gigabit): na forma de um conector RJ45 na parte de trás, mas também se ramifica para uma placa-filha sem fio, fornecendo conexões Wi-Fi 802.11b/g e Bluetooth 2.0.

- Um leitor de cartões múltiplos: fornece slots para Memory Stick, SD, MultiMediaCard (MMC), Microdrive e Compact Flash.

Equipamentos com “menos fios”

Graças à ampla adoção da tecnologia Blutetooth, os controles com fio se tornaram coisa do passado. A nova versão do controle Dualshock 2 do PS2 foi chamada de Sixaxis (seis eixos, em tradução livre) e, embora não seja a mudança radical que outra fabricante decidiu seguir, apresenta um giroscópio para novos tipos de interação. Entretanto, isso ocorreu removendo o feedback tátil (vibração). Um ano depois, a Sony surpreendeu os jogadores com o Dualshock 3, que restaurou o motor tátil.

Uma outra novidade, agora é possível ligar o console pelo controle sem fio.

Interfaces internas

Com relação aos componentes internos, a SouthBridge se conecta a:

- Starship 2: um adaptador para duas memória Flash NAND de 128 MB. Nos bastidores, o Starship faz a ponte entre o barramento local da Southbridge e o protocolo padronizado “Common Flash Interface Protocol” (amplamente adotado para a interface de memória Flash) [44]. O PS3 armazena o sistema operacional nesses chips, entre outras coisas.

- O chipset do PlayStation 2: no canto da placa-mãe, há um chip chamativo que abriga nada menos que o Emotion Engine e o Graphics Synthesizer. A combinação EE+GS se conecta a 32 MB de RDRAM e uma ponte de E/S (nomeada “ponte PS2”), que juntas formam cerca de 90% do PlayStation 2 original.

- O chip EE+GS envia o sinal de vídeo diretamente para o RSX.

- Esses chips não são acessíveis pelos desenvolvedores, eles são usados apenas para a retrocompatibilidade!

Retrocompatibilidade

Tendo mencionando os chips do PS2, suponho que seja hora de falar sobre a retrocompatibilidade do PlayStation 3 de uma vez por toda.

Primeiramente, deixe-me explicar como a retrocompatibilidade geralmente funciona: os consoles podem reproduzir os jogos de seus predecessores com a ajuda do software (instruindo o hardware existente a se comportar como o console antigo) e do hardware (onde o hardware existente fornece retrocompatibilidade total ou parcial; e/ou a empresa adicionou chips extras para recriar o sistema antigo dentro da nova placa-mãe). Com a quantidade de poder de processamento que o PS3 apresenta, seria de se esperar que a Sony colocasse um emulador de PS2 rodando dentro do Cell e acelerado pelo RSX. Bem, por alguma razão, isso não aconteceu e, em vez disso, a Sony encaixou o conjunto de chips do PS2 em um canto da placa-mãe.

Por outro lado, os chips ausentes que não eram críticos (IOP, SPU, etc.), foram replicados via software e rodavam no Cell. No caso dos salvamentos de jogos, inicialmente, os usuários precisavam adquirir um adaptador para o memory card, mas, após uma nova atualização de software, os memory cards começaram a ser emulados como imagens de disco armazenadas no disco rígido, enquanto o Magic Gate (o sistema de criptografia) era manipulado perfeitamente por uma SPU.

Como o Cell e o RSX ficam ainda “ativos” durante a reprodução de um jogo de PS2, o sistema oferece dois métodos de redimensionamento para aumentar a resolução da tela durante o jogo. Os métodos são “vizinho mais próximo” ou “suavizado” (antisserrilhamento).

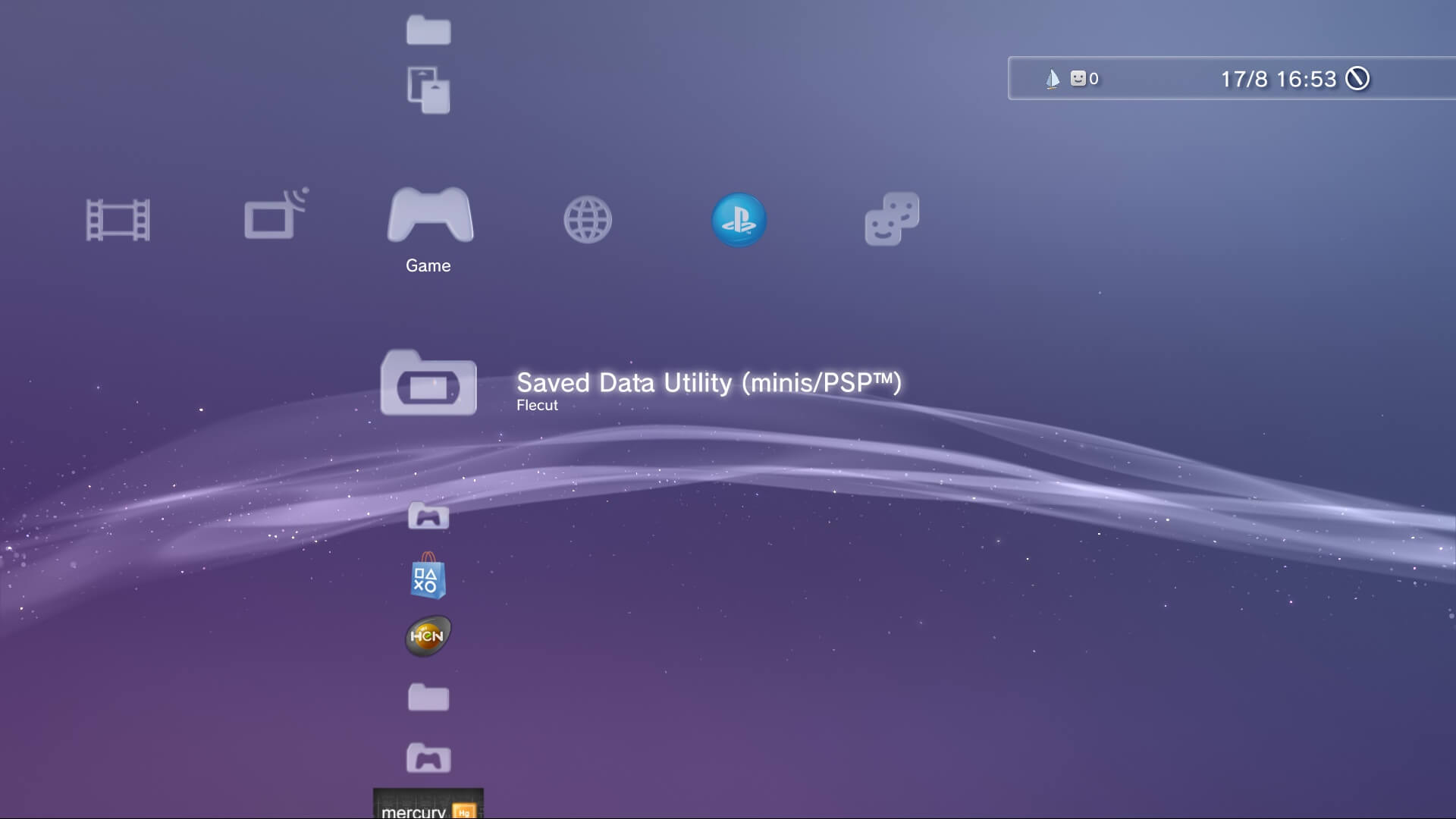

(Nâo se preocupe com os outros ícones por enquanto, pois alguns nem são oficiais).

Em resumo, graças a essa configuração, o PS3 roda jogos do PS2 com um nível de compatibilidade impressionante. Além de tudo, você pode aproveitar os novos recursos que vêm com o novo console (controle sem fio, interface HDMI e cartões de memória virtual).

Como se não bastasse, os jogos de PS1 também podem ser executados, desta vez sem precisar incorporar o antigo SoC ou GPU (ele depende de software de emulação pura).

O estranho fim da retrocompatibilidade via hardware

Ao longo do ciclo de vida do PS3, a Sony lentamente removeu os chips exclusivos do PS2 da placa-mãe do PS3, chegando ao ponto em que a retrocompatibilidade fosse apenas feita através software de emulação (com maiores limitações, como apenas rodar jogos de PS2 adquiridos em sua loja online). Como a Sony nunca substituiu o chipset do PS2 (como havia feito anteriormente com o hardware do PS1 dentro do PS2), faz você se perguntar sobre o racional técnico e executivo por trás disso. Bem, como um estudo de caso, aqui está minha opinião rápida sobre os motivos para isso:

- Momento: é provável que a Sony tenha planejado que os proprietários de PS2 comprassem seu novo produto como substituto do atual, já que isso é mais acessível para os consumidores (eles podem vender seu antigo sistema). No entanto, por algum motivo, a Sony não havia preparado um software de emulação antes do dia do lançamento, então inicialmente recorreu à adição de chips extras. Depois, à medida que o software de emulação progredia satisfatoriamente, eles gradualmente removeram esses chips em revisões posteriores da placa-mãe.

- Para complementar, o desenvolvedor “M4j0r” comentou: “Um ponto interessante pode ser que a Sony desenvolveu as duas revisões de emulação via hardware simultaneamente (EE/GS e GS somente), acredito que alguns jogos rodam melhor dependendo de qual você usa” [45].

- Custos: o preço inicial da primeira revisão do console (CECHA, apenas no Japão e EUA) em 2006, que era compatível com o PS2, foi fixado em US$ 599,99 ou ¥60.000,00 sem impostos (£425,00 em 2020 com correção da inflação) [46]. O modelo seguinte (CECHC, lançado em 2007 internacionalmente) removeu o Emotion Engine e a RDRAM (transferindo essas tarefas para o software de emulação) e foi lançado no Reino Unido com um preço de etiqueta de £425,00 (£603,00 em 2020). Mais tarde, no mesmo ano, a Sony lançou um novo modelo (CECHG) sem nenhum chip do PS2 por £126 a menos [47]. Tudo isso prova que a retrocompatibilidade é, no final, uma funcionalidade cara.

- Hardware ocioso e desperdício de energia: embora o Cell e o RSX ainda executem algumas tarefas para recriar o ambiente original, estas são mínimas em comparação com o seu potencial total. Combinado com o fato que os modelos CECHA têm um consumo de energia acumulado de 399 Watts [48], faz você se perguntar se este projeto vale o consumo de energia, muito menos eficiente (para comparação, a nova fonte de alimentação do CECHG consome 285 Watts).

- Eu entendo que existem outros fatores envolvidos na redução do consumo de energia, como as novas revisões do Cell e do RSX. Contudo, ainda acredito que o chipset do PS2 desempenhou um papel importante.

- Inflexibilidade: o chip EE+GS não é reprogramável, o que significa que o resultado final sempre será o mesmo, independentemente de haver falhas ou possíveis melhorias. Compare isso com as melhorias gráficas do emulador PCSX2 [49] e suas capacidades de modificação [50], isso nos mostra que há espaço para melhorias que são possíveis e apreciadas.

Pessoalmente, acredito que a emulação puramente via software seja a opção mais viável a longo prazo devido à sua escalabilidade, personalização e independência de hardware proprietário. Mas é claro que isso exige mais esforço para ser implementado com precisão, como demonstra o contínuo desenvolvimento do PCSX2 por uma comunidade de voluntários (observe que o mencionado emulador só roda em PCs x86).

Compatibilidade lateral

Ainda não terminamos de falar sobre compatibilidade! Você pode ficar surpreso que a Sony permitiu que os usuários jogassem um subconjunto de jogos do PlayStation Portable. Embora a emulação tenha sido realizada completamente via software, assim como a compatibilidade com o PS2 em modelos posteriores.

Como não há nenhum leitor de disco UMD no PS3, os usuários devem acessar um catálogo de jogos da loja online da Sony para baixar e instalar qualquer jogo do PSP.

Sistema Operacional

Agora que os consoles domésticos se tornaram poderosas centrais multimídias, foi necessário ter um sistema operacional mais complicado para fornecer aos usuários mais serviços e jogos com uma camada maior de abstração. Tudo isso, mantendo a segurança e o desempenho adequado.

Consequentemente, termos como shell ou BIOS não são mais usados para descrever esta área, não porque não existem mais, mas devido descreverem apenas uma pequena fração do novo sistema. O termo genérico agora é “sistema operacional”, que compreende muitas áreas (carregador de inicialização, kernel, interface do usuário) analisadas separadamente. Como sempre, recomendo verificar o sistema operacional do PSP primeiro, já que seu projeto modular é um ingrediente recorrente no PS3.

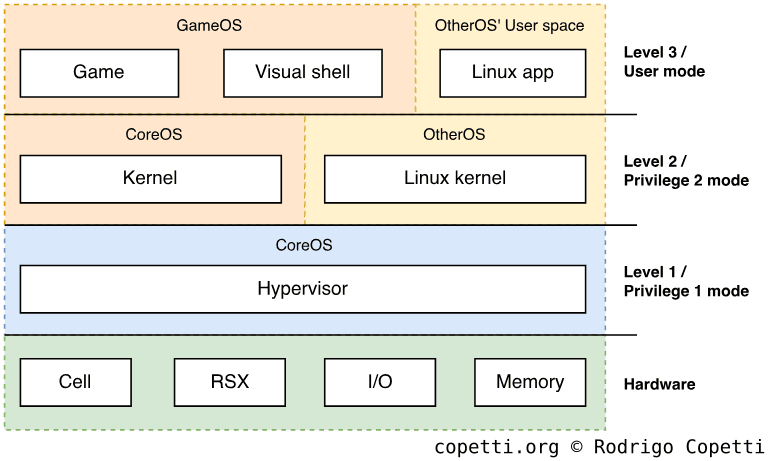

Níveis de privilégio do Cell

Antes de entrarmos em detalhes, preciso mencionar os diferentes modos de operação no Cell. Eu originalmente planejava descrever isso na seção “CPU”, mas como aquela seção ficou incrivelmente densa, vou apresentá-lo aqui onde você verá seu uso prático imediatamente. Além disso, seus modos também afetam o projeto de qualquer sistema operacional que execute dentro do Cell — não apenas o que a Sony desenvolveu para o console.

Dito isso, para proteger contra o acesso não autorizado aos dados e/ou recursos sensíveis, o Cell implementa um conjunto de níveis de privilégio herdado da especificação PowerPC. Em outras palavras, o Cell executa os programas em dois modos:

- Modo privilegiado: o Cell concede acesso a todos os cantos do seu hardware (registradores, endereços de memória, instruções, etc.) [51]. Por razões de segurança, este modo só deve ser usado pelo núcleo do sistema operacional (ou seja, o Kernel).

- Além disso, o Cell foi projetado para executar vários sistemas operacionais simultaneamente e para alcançar isso no nível de hardware, o “modo privilegiado” pode ser dividido em dois subníveis: Privilegiado 1 e Privilegiado 2. O “Privilegiado 2” é destinado a ser usado por um Kernel, enquanto o “Privilegiado 1” é usado por um Hypervisor, este último arbitra recursos entre diferentes Kernels que executam simultaneamente.

- A funcionalidade “hypervisor” também se tornou uma área de pesquisa na sede da IBM [52] [53].

- Modo usuário: como o nome indica, o Cell concede apenas um conjunto limitado de recursos [54] e é direcionado para aplicativos tradicionais que rodam em cima do sistema operacional. Se por algum motivo, um programa solicitar acesso a um local protegido, então a execução é direcionada ao Kernel ou Hypervisor para decidir se o acesso deve ser concedido ou não.

Além disso, os SPEs contêm um modus operandi chamado modo isolado e ele protege o processo a execução dentro da SPU, de modo que nenhuma unidade externa (o PPE ou outros SPEs) possa acessá-la até que a SPU termine. O modo isolado pode ser ativado após o envio de um programa para qualquer SPE e garante que o processador não seja alterado enquanto um código sensível (ou seja, uma rotina de criptografia) está executado.

O sistema operacional da Sony, que descreverei nos parágrafos a seguir, usa todos os modos descritos para lidar com sua segurança.

Visão geral

Como eu disse antes, o sistema operacional é bastante complexo. Portanto, para podermos seguir esta seção sem muita dificuldade, podemos dividir o tipo de arquivos que encontraremos no sistema operacional do console em camadas diferentes:

- Loaders (carregadores): para resumir, os programas/binários nesse console são sistematicamente criptografados. Assim, os “Loaders” são programas que executam programas “reais”. Em outras palavras, os Loaders pegam os binários, descriptografam, verificam sua autenticidade e, finalmente, enviam para o respectivo processador (o PPE ou SPE) para execução. Se isso não parece complicado, os Loaders são ligados em cadeia para proteger ainda mais o software. Finalmente, os Loaders são encontrados em muitas mídias.

- Alguns Loaders são atualizados pela Sony (por meio de atualização de software), enquanto outros não podem ser alterados. Isso é independente de serem instalados em armazenamento regravável, já que alguns Loaders são criptografados usando chaves específicas do console, então não podem ser alterados depois que o console sai de fábrica (ao menos pelos meios tradicionais).

- System files (arquivos de sistema): esses compreendem de binários de baixo nível (executados através de Loaders), metadados para organizar o hardware, utilitários e outros recursos (ou seja, fontes, imagens). Assim como os Loaders, há arquivos de sistema específicos do console que não podem ser substituídos ou gerados automaticamente.

- Alguns binários pegaram emprestado o código dos projetos FreeBSD e NetBSD [55].

- User Content (conteúdo de usuário): esses incluem arquivos de configuração (por exemplo, configurações da internet), dados usados por jogos (por exemplo, arquivos de instalação e salvamento de jogos) e dados gerados automaticamente pelo console (por exemplo, informações de disco rígido).

- Ao contrário das outras camadas, a destruição desses dados não leva a resultados catastróficos.

Hierarquia de segurança do sistema operacional

Em termos gerais, o sistema operacional do PS3 é projetado com a mesma abordagem modular do PSP. Relembrando do artigo anterior, o sistema operacional é composto de vários módulos. Esses podem servir ao usuário (como um jogo ou aplicativo) ou residir na memória indefinidamente para servir outros módulos (na forma de chamadas de sistema e/ou drivers). Alguns módulos têm mais acesso privilegiado do que outros (módulo do Kernel versus módulo do usuário).

Referência ao “OtherOS” são explicadas com mais detalhes nas próximas seções.

O sistema operacional, durante seu ciclo de vida, chamará muitos módulos com diferentes privilégios. A Sony construiu seu sistema operacional para que os módulos rodem nos três níveis de privilégio do Cell:

- Nível 1: aqui é onde reside um Hypervisor programado pela Sony. Também referido como

lv1, este programa é a porta para cada bit do console e vinculado as exceções acionadas pela MMU. Dito isso, o hypervisor só aceita solicitações de programas autorizados pela Sony (residentes no próximo nível de privilégio). Enquanto o Hypervisor reside na memória, ele também fornece chamadas de sistema de baixo nível e suporte ao sistema de arquivos FAT16. - Nível 2: naturalmente reservado para o Kernel, um programa privilegiado também chamado

lv2ou “Supervisor”. O Kernel abstrai o hypervisor para que os programas do nível 3 não tenham interação direta com ele. O Kernel fornece funções de multithreading tanto para PPU quanto para SPU. Por fim, o Kernel inicializa os módulos do espaço do usuário. - Nível 3: o restante dos programas (chamados espaço do usuário), incluindo jogos e a interface visual, são executados neste nível. Estes programas estão sob o controle do Kernel para se comunicar com o hardware do console e não podem criar processos/programas novos unilateralmente.

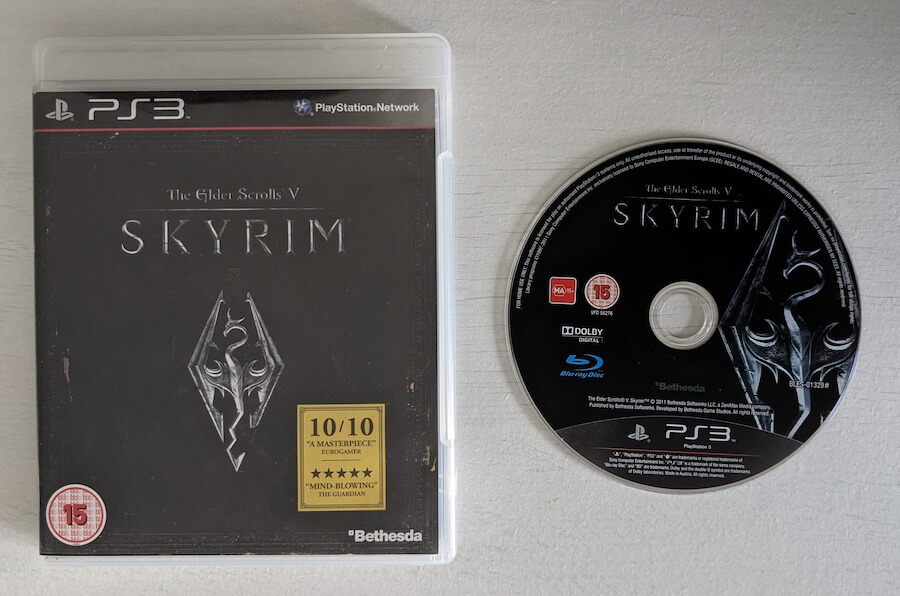

Mídia de armazenamento

Com tudo isso dito, onde todos esses dados são armazenados? Do ponto de vista do usuário comum, existem apenas dois meios visíveis: os discos Blu-ray para jogos e um disco rígido para saves. Bem, existem mais alguns, então vamos dar uma olhada em cada um deles agora!

BootROM do Cell

Acontece que dentro do Cell há uma pequena ROM escondida em algum lugar que os fabricantes podem usar para armazenar um boot-loader (carregador de inicialização) “protegido”. A IBM fornece esse espaço para poupar as empresas (não apenas a Sony) de terem que implementar manualmente seus próprios métodos de ofuscação de código para proteger seu código de inicialização, já que os componentes disponíveis comercialmente nem sempre estão preparados para suas necessidades específicas.

Como essa memória já está fisicamente protegida com ofuscação de código, ela não precisa ser criptografada. Desta forma, ela é ideal para um boot-loader de primeiro estágio (que não pode ser criptografado) e o PlayStation 3 armazena seu estágio inicial de inicialização nela.

Memória Flash NAND/NOR

Lembre-se daquelas 256 MB de memória flash NAND que mencionei brevemente antes? Bem, é aqui que fica a maior parte do sistema operacional. Isto é, era até que a Sony lançou o modelo CHECHH no final de 2007, substituindo as NANDs de 256MB por uma NOR de apenas 16 MB. Como consequência, alguns arquivos tiveram que ser movidos para outro lugar. Para fins de simplicidade, vamos primeiro ver o que esses chips armazenam [56]:

- Carregadores específicos do console: especificamente, dois carregadores chamados

bootldremetldr. Esses arquivos são criptografados com uma chave gravada durante a fabricação, portanto, não podem ser substituídos!- Seja como for, existem funções ocultas no hipervisor da Sony que permitem atualizá-los, embora, por alguma razão, nunca tenham sido usadas [57].

- CoreOS: a primeira metade do sistema operacional. Consiste principalmente em mais carregadores que continuarão o processo de inicialização e, eventualmente, a inicialização a segunda metade (GameOS). O CoreOS também fornece o menu de recuperação, um shell alternativo que contém os utilitários de manutenção que os usuários podem usar para (tentar) reparar seu console.

- IDs únicos: semelhantes ao IDStorage do PSP, eles são usados pelo console para controlar o hardware protegido como a unidade de Blu-ray; ou pela Sony para autenticar o console em seus servidores online (ou seja, a chave IDPS).

- Recursos de segurança: alguns programas dependem deles para executar operações de segurança. Por exemplo, filmes em Blu-ray com DRM verificam um bloco chamado Virtual Table Rights Management (VTRM — tabela virtual de gestão de direitos, em tradução livre). A Sony também armazena ferramentas de revogação e registros para fazer uma lista negra de certificados de segurança que foram comprometidos no passado.

Devido ao seu tamanho maior, os modelos com memória Flash NAND também armazenam a parte restante do sistema operacional (chamada de GameOS ou devflash). Isso inclui:

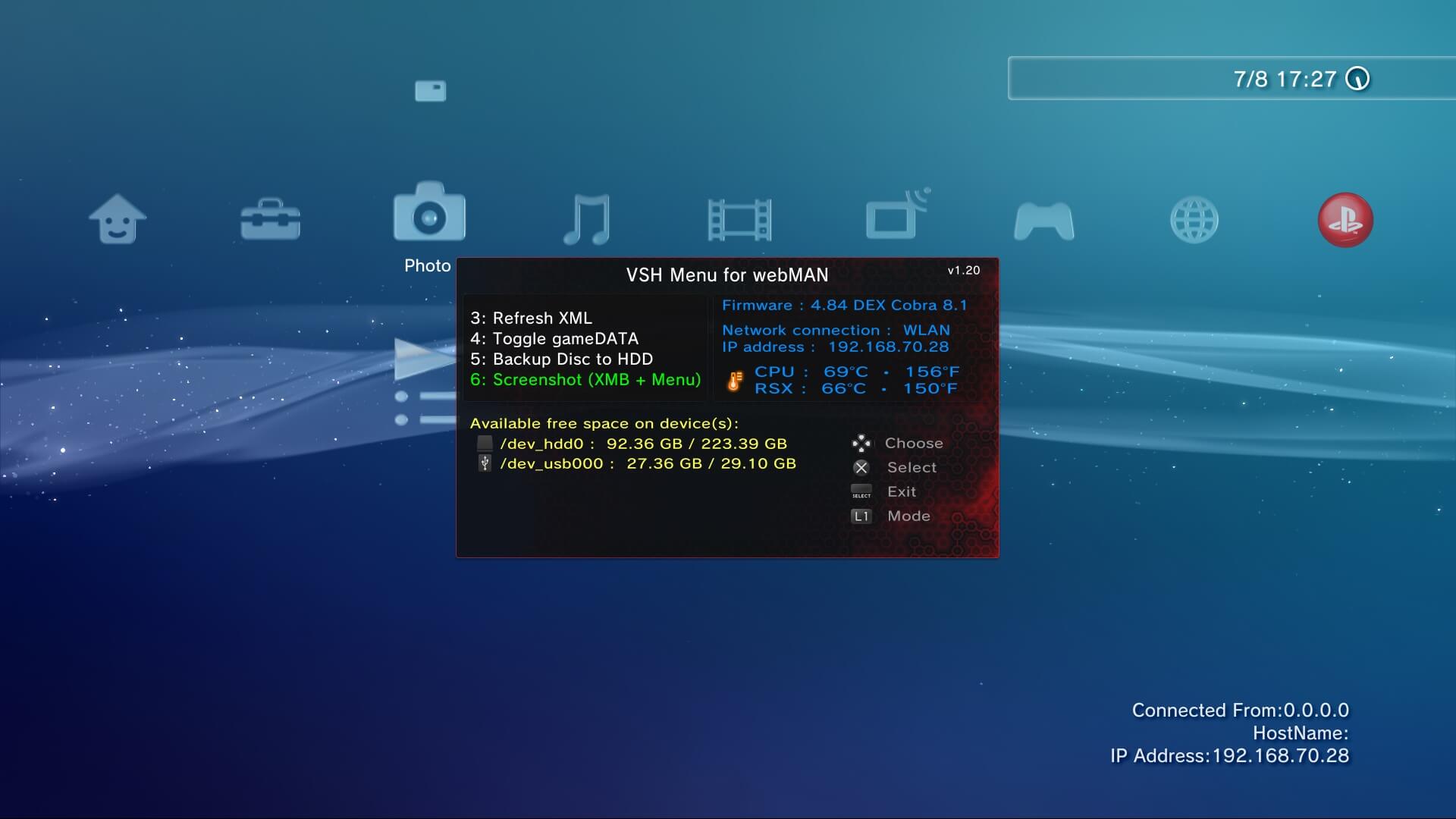

- A Interface Visual (VSH, de Visual Shell): uma continuação da interface característica do PSP, também é fornecida com toneladas de módulos (plugins) e recursos.

- Emuladores: programas mencionados anteriormente que permitem que o PS3 execute jogos de PS1, PS2 ou PSP. O emulador específico do PS2 carregado depende da revisão do console (se ele tem o hardware completo do PS2, ou o hardware parcial do PS2, ou se não tem nenhum hardware do PS2).

- Bibliotecas de tempo de execução: programas desenvolvidos com o SDK da Sony são vinculados dinamicamente a um conjunto de bibliotecas armazenadas aqui.

- Reprodutor de Blu-ray: programas que lidam com a interação com a unidade de Blu-ray e a decodificação de filmes.

- Recursos do sistema: como fontes e certificados nos quais os binários dependem para funcionar.